Canadair Bit Synchronizer

Theory of Operation

28 January 1991

# Theory of Operation

# Table of Contents

| 1.0 | Introduction |      |                  |    |          |

|-----|--------------|------|------------------|----|----------|

|     | 1.1          | Data | Synchronization: | An | Overview |

- 2.0 Design Goals

- 3.0 Design Methodology for the Canadair Bit Synchronizer

- 3.1 Voltage Controlled Oscillator

- 3.1.1 Capture Range Impliations Upon VCO Center Frequency Accuracy

- 3.1.2 Phase Noise Requirements

- 3.2 Transition Tracking Phase Detectors

- 3.3 Loop Filter and Loop Parameters

- 3.4 Matched Filter

- 3.4.1 Filter Selection for NRZ Symbols

- 3.4.2 Mismatch Loss for Manchester Symbols

- 3.5 Lock Detection

- 4.0 Detailed Design

- 4.1 Matched Filter

- 4.2 Loop Filter & Phase Detector

- 4.3 VCO

- 4.4 Lock Detection

- 5.0 Measured Bit Synchronizer Performance

- 6.0 Accomodating Other Data Rates and Requirements

- 7.0 Schematics and Parts List for Canadair Bit Synchronizer

- 8.0 Recommended Alignment and Trouble-Shooting Methods

# Canadair Bit Synchronizer Theory of Operation

bу

# James A. Crawford R&D December, 1990

#### 1.0 Introduction

The document which follows is intended to provide detailed information about the Canadair bit synchronizer design approach, the theory behind the design, and where possible, information relevant to design modifications which would make the same generic design suitable for other as yet undefined systems. Although the Canadair system utilizes bi-phase (Manchester) modulation, the bit synchronizer is designed as an NRZ bit synchronizer per Loral direction. The Manchester signal is then viewed as an NRZ data stream at a bit rate twice that of the true Manchester symbol rate. Aside from a later section which addresses the incurred system mismatches which result when using an NRZ synchronizer to synchronize Manchester signals, this document will discuss the subject in terms of NRZ symbols rather than Manchester symbols.

Actual performance of the synchronizer in the Canadair system is further complicated compared to the theory presented here because the baseband data stream is impressed upon a subcarrier using frequency modulation, then combined with a wideband baseband video signal, and the result used to frequency modulate an RF carrier signal. Any nonlinearities, be they due to modulators or insufficient RF demodulators, or bandwidths resulting degradation of the RF waveform, will cause video energy to be folded into the baseband spectrum region occupied by the databearing FM subcarrier thereby deteriorating the effective signalto-noise (SNR) ratio of the data channel. These added dimensions of the overall Canadair system will not be considered here. Rather, the bit synchronizer will be discussed strictly in the context of a linear, additive white Gaussian noise (AWGN) baseband channel.

### 1.1 Data Synchronization: An Overview

The bit synchronizer is responsible for i) extracting high quality data bit estimates and ii) data clock estimates from the incoming analog signal which is generally buried in noise. Since both of these functions are extremely important in order for the overall system to perform well, design of the bit synchronizer portion of the system carries substantial importance.

Bit synchronizer design must be viewed as a marriage between

a good understanding of communication theory and hardware design if near optimal performance is to be obtained. Many different methods are available for performing the bit synchronization function. Reliable determination of whether synchronization has in fact been obtained is an equally difficult problem, particularly if the synchronization process must be performed quickly. It is straight forward to show that the design of the synchronization (or lock) detector is intimately tied to the false-lock indication probability which the system can accommodate. Due to the large amount of material available on the subject of bit synchronization, we will be brief and only address several of the many approaches which are available and which are suitable for the range of data rates which are of interest (10 kbps to 2 Mbps).

A nice introduction to optimal bit synchronization can be found in [23-28]. Gardner [2] divides the subject into estimation theoretic (e.g. maximum likelihood), early-late gate, transition tracking, and other categories. The early-late gate approach is primarily intended for use with square pulses where the SNR is very high. We will not consider it further since it is also not suitable where rapid synchronization is required. Holmes [24] itemizes a number of suboptimal bit synchronizers which are based upon either delay-and-multiply or upon the use of a nonlinearity to obtain a clock component.

#### Estimation Theoretic

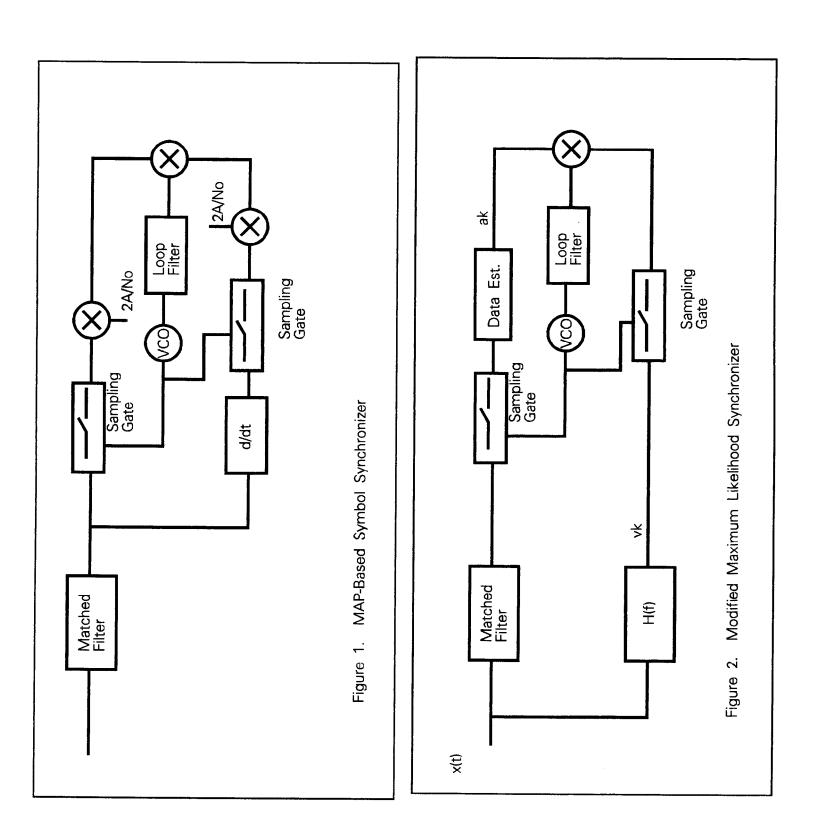

Methods grouped into this category are generally capable of near optimal performance and are primarily based upon maximum-likelihood (ML) or maximum a posteriori (MAP) criteria. The MAP-based synchronizer (no intersymbol interference, ISI) is considered in great detail in [25] and an actual detailed implementation is discussed in [36]. A fairly broad range of theoretic-based synchronizers are derived in [29-35].

The MAP-based synchronizer discussed in [36] is shown in Figure 1. It is quite straight forward to show [25] that the log-likelihood function in this case is given by

$$\Lambda(\tau) = C_1 \sum_{n} Log \cosh \left[ \frac{2A}{N_o} y(\tau) \right]$$

(1)

where

C<sub>1</sub> a constant

A peak signal amplitude, volts

N<sub>o</sub> one-sided noise power spectral density, W/Hz

y(\tau) sampled output of matched-filter output

t symbol timing estimation error

z(t) input signal

h(t) matched-filter impulse response

T<sub>s</sub> symbol period

T<sub>o</sub> observation period

and

$$y(\tau) = \int_{0}^{T_{o}} z(t) h(t-nT_{s}-\tau) dt$$

(2)

It is simple to maximize the likelihood ratio (since log() is a monotonic function) simply by differentiating (1) to give

$$\frac{\partial \Lambda(\tau)}{\partial \tau} = C_1 \sum_{n} \left[ \frac{2A}{N_o} \dot{y}(\tau) \tanh \left( \frac{2A}{N_o} y(\tau) \right) \right]$$

(3)

The loop configuration shown in Figure 1 clearly drives the quantity given by (3) to zero in steady-state.

The modified maximum likelihood (MML) synchronizer discussed in [33] is shown in Figure 2.  $H_{\rm MF}$  represents the matched filter whereas H(f) is a filter designed to extract the data sampling clock. In cases where the matched filter output pulse shape is Nyquist (i.e. no ISI), H(f) simplifies to

$$H(f) = H_{MF}(f) \left[ j2\pi f - \sum_{m} \frac{\dot{r}(mTs)}{r(0)} e^{-j2\pi f mT_{s}} \right]$$

(4)

which is nothing more than the derivative of the matched filter output followed by a transversal filter. In the case where all the derivatives of r(t) are zero at t=m  $T_s$ , this reduces to the ML synchronizer.

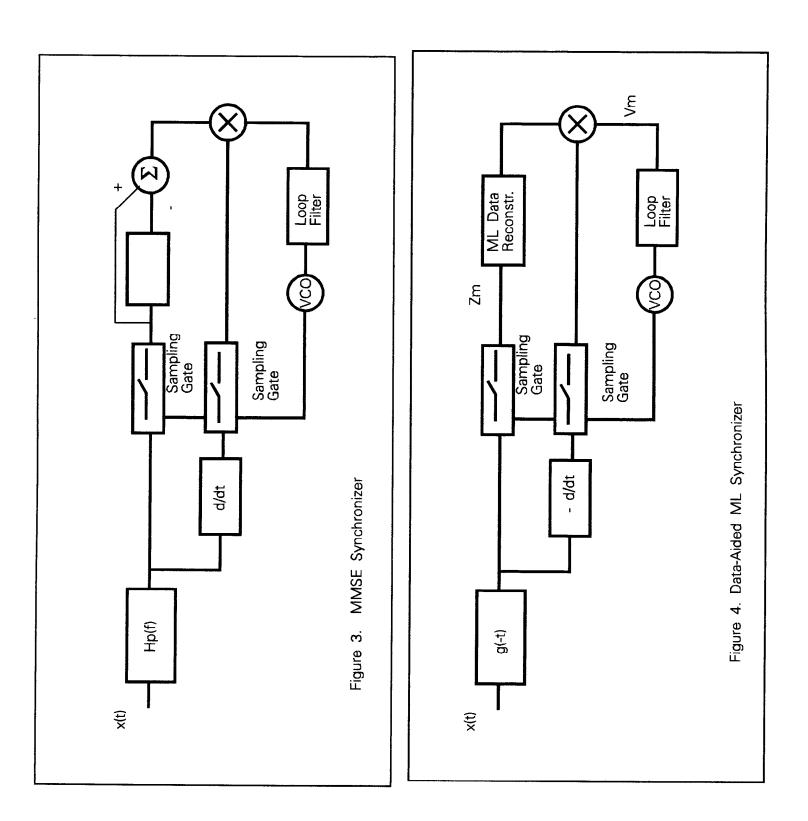

The minimum mean-squared error (MMSE) synchronizer is shown in Figure 3. In this case,  $H_p(f)$  eliminates the ISI as well as maximizes the SNR at its output. Since the ISI has been eliminated, the data reconstruction is very simple. If the output pulse is again Nyquist,  $H_p(f)$  reduces to the matched filter  $H_{NF}(f)$ . In situations where the bandwidths involved are considerably less than Nyquist, the MMSE method is preferred compared to the MML method [33].

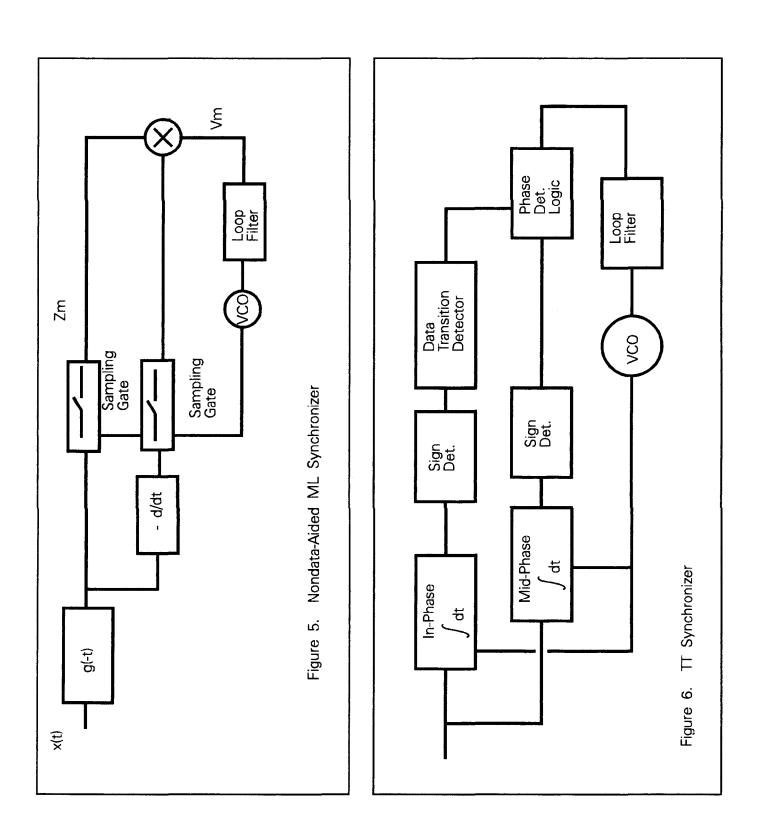

The data-aided ML and non-data-aided ML synchronizers are analyzed in [35] and are shown in Figures 4 and 5. If no ISI is present at the output of the matched filter g(-t), then the ML data reconstructor reduces to a simple comparator in which case it looks

very similar to Figure 3. If ISI is present, the optimal data reconstructor for the AWGN channel is a Viterbi receiver.

These previous four synchronizer types are compared in [34] for the case of raised-cosine symbols. Unlike in the sited references, [34] considered using each synchronizer to perform the timing recovery (only) and the data estimates were made using a matched filter followed by a maximum-likelihood sequence estimator [22]. As far as data estimation goes, this is optimal.

For the small excess bandwidth situation which is generally applicable in our situation, the smallest mean-square synchronization error for low SNR occurs for the DA-ML synchronizer [34]. Although this may be true, further examination of other plots in [34] shows that much larger synchronization loop bandwidths may be used for the MML and MMSE synchronizers in contrast hence making these approaches more suitable where fast acquisition is a necessity.

The methods addressed here are clearly numerically intensive, particularly at high data rates. As a result, they were not considered further in the context of the present design.

#### Transition Tracking

Transition tracking symbol synchronization is discussed in nearly every basic text convering bit synchronization including [21,23,24,26,28,29] to name but a few. A particularly good reference on the subject is [37]. A block diagram for a transition tracking (TT) symchronizer is shown in Figure 6. Note that the matched filter which was common to all of the previous synchronizers is missing. It is in fact present in the form of the in-phase and mid-phase integrators in the case of square NRZ data symbols.

Of the synchronizers considered thus far, the transition tracking synchronizer is the best suited for the Canadair system because it is very robust [37] and the most simple to implement. The approach may be used at virtually any data rate as well, making it an excellent choice for a generic bit synchronizer topology.

### 2.0 Design Goals

On August 7, 1990, a kick-off meeting was held to identify the design goals for the synchronizer. Tenative design goals were identified as shown in Table I.

# Table I. Canadair Bit Synch: Initial Design Goals

Power Supplies ±15, 5 volts

Temperature Range -55 to +85 C

NRZ Data Rate 40 kbps (capable of 1 kbps to 2 Mbps

with component value changes)

Waveforms Bi-phase-L, NRZ-L

Lock Time < 100 symbols at TBD  $E_b/N_o$

Run Length > 30 symbols

Capture & Track Range  $\pm 1$  % desired, actual TBD at TBD  $E_b/N_o$

Min Capture SNR 12 dB desired, actual TBD

Bit Error Rate ≤ 3 dB from theory at TBD bit error rate

Clock Jitter < 0.1% rms at TBD  $E_b/N_o$

The original Canadair synchronizer was to be 40 kbps NRZ. Early into the project however, difficulties were identified involving DC offset out of the subcarrier demodulator and the waveform was changed to Manchester. Ranging precision considerations were also a factor in this decision. The minimum data rate was later raised to 10 kbps from 1 kbps. The design goals which have been adopted for the bit synchronizer are provided in Table II.

# Table II. Canadair Bit Synch: Adopted Design Goals

±15, 5 volts Power Supplies

Temperature Range -55 to +85 C

(capable of 10 kbps to 2 Mbps 80 kbps NRZ Data Rate

with component value changes)

NRZ 30% to 100% Transition Density

Bi-phase-L, NRZ-L, ± 1 volt peak-peak Waveforms

input

NRZ: Lock Time

< 200 symbols at 12 dB  $E_b/N_o$ ,  $\Delta R=0$

< 600 symbols at 12 dB  $E_b/N_o$ ,  $\Delta R=\pm 0.5\%$

Bi-phase:

< 150 symbols at 12 dB  $E_b/N_o$ ,  $\Delta R=0$ < 450 symbols at 12 dB  $E_b/N_o$ ,  $\Delta R=\pm 0.5\%$

Run Length > 30 symbols

$\pm 1$  % at 6 dB  $E_b/N_o$ Capture & Track Range

12 dB Min Capture SNR

$\leq$  3 dB from theory at 10<sup>-5</sup> BER Bit Error Rate

< 0.5% at 12 dB  $E_b/N_o$ Clock Jitter

AR denotes data rate error, bps

The design is primarily driven by the bottom six items shown in Table II. Lock time as we'll discuss shortly, is strongly driven by the prevaling data rate error and signal to noise ratio. It is fairly meaningless to discuss lock times on the order of Table I (100 symbols) unless the data rate error is very small and the SNR is very high. Since Mike Landry believed that the acquisition process could take as long as 500 to 600 symbols before there would be any system impact, the 100 symbol figure was changed to the values shown in Table II. Definition of what is meant by "lock time" is also at issue here. As alluded to in the introduction, reliable determination of lock is in itself a difficult question. In the Canadair bit synchronizer, indication of synchronization is substantially later than when synchronization is actually obtained. The run length parameter primarily sets a limit on the maximum number of consecutive data-ones or data-zeros which may occur and thereby affects the choice of synchronizer loop bandwidth. (This is not the case with Manchester symbols where we are guaranteed a transition every symbol period.) Extremely long run length capability and fast acquisition are generally mutually exclusive design requirements. Normally, capture and track range are specified separately; they are also a strong function of SNR. In lieu of firm requirements, the  $\pm 1$  % requirement was taken as a noise free design goal.

It cannot be understated how much the data rate uncertainty parameter amplified the complexity of the bit synchronizer design. Since VCXOs cannot cover this wide frequency range, and LC oscillators are prone to temperature drift, the bit synchronizer oscillator design case was quite involved. Had the data rate uncertainty been roughly  $\pm 0.07$  % or less, the size of the present design would have shrunk dramatically (at least 50%). The worst-case locking speed would also be substantially faster as well.

The minimum capture SNR of 12 dB presents no serious design challenges unless very fast locking is desired over the full  $\pm 1$  % data rate uncertainty range. The data rate anomoly for Canadair should be much smaller than  $\pm 1$  % which should result in good locking speed nonetheless. Since the design is also required to accomodate NRZ data rate requirements up to 2 Mbps, this also dictated that the VCO phase noise performance be fairly good.

The degradation with respect to theory of 3 dB for the NRZ waveform is also very obtainable. The synchronizer design for Canadair is capable of performing within 1 dB of theory or better for NRZ data provided that the premodulation and matched filter are done properly and if no additional bandlimiting by other system elements is present.

Finally, the recovered clock jitter requirement is difficult enough that careful tracking loop parameters had to be selected. This is discussed at some length in section 3.3.

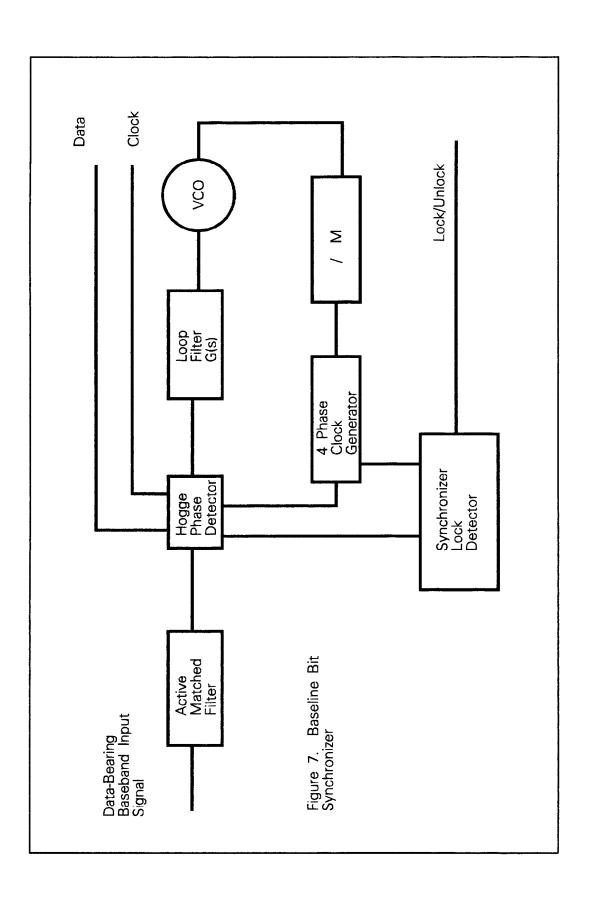

# 3.0 Design Methodology for the Canadair Bit Synchronizer

A block diagram for the bit synchronizer is shown in Figure 7. We will discuss each of the major functional areas shown in some detail within the balance of this section, identifying required design goals as they surface.

# 3.1 Voltage Controlled Oscillator

The VCO for the Canadair bit synchronizer occupies roughly half the total board area in the final configuration and simply based upon this proportion, is a pivotal design consideration for the synchronizer. As alluded to earlier, the primary parameter driving the complexity of this function is the desire to be able to accomodate data rate anomolies as large as ±1 % while having adequate phase noise performance to support NRZ data rates up to 2 Mbps.

The bit synchronizer effectively phase-locks the VCO to the data transitions of the incoming NRZ data stream. Two of the primary areas which must be addressed are i) center frequency accuracy and ii) phase noise performance. We can obtain some useful insight into the center frequency accuracy requirements using the simple arguments presented next.

# 3.1.1 Capture Range Implications Upon VCO Center Frequency Accuracy

A high degree of VCO center frequency accuracy is required in the bit synchronizer in order to avoid the need for a large closed-loop bandwidth during the acquisition process. A second alternative to the large acquisition bandwidth is of course to perform an acquisition sweep search using a smaller loop bandwidth, but this is not without its complications. In the next few paragraphs, we will examine the needed loop bandwidth requirements for acquisition as driven by VCO center frequency misalignment.

In the present context, the symbol shape which reaches the bit synchronizer input will be quite smooth due to the Bessel prefiltering which is performed at the transmitter. If we assume that a square-root raised cosine pulse with excess bandwidth factor 0.5 is representative for this situation, it can be shown that a N=3 Butterworth lowpass filter with BT= 0.5 is less than 0.5 dB from theory at a bit error rate (BER) of 10<sup>-5</sup>. The (one-sided) noise bandwidth for this filter is given by

$$B_n = \frac{f_c}{\frac{2n}{\pi} \sin(\frac{\pi}{2n})} Hz \tag{5}$$

where  $f_c$  is the filter 3 dB corner frequency (Hz) and n is the filter order. Therefore, for a N=3 Butterworth filter,

$$B_n = 1.047 \ f_c = 1.047 \ x \ 0.5 \ x \ R$$

$$= 0.524 \ R \ Hz$$

(6)

where R is the NRZ symbol rate in bits per second. The variance of the noise at the matched filter output is given by

$$\sigma_n^2 - N_o B_n - 0.524 N_o R \tag{7}$$

where  $N_{\circ}$  is the one-sided noise power spectral density (W/Hz). The effective variance seen by the tracking loop will be much less than this quantity since the (one-sided) loop bandwidth  $B_{\rm L}$  is generally much less than  $B_{\rm n}$ .

Assuming an alternating 1/0 data stream, the input signal has the appearance of a sine wave embedded in noise where the energy per bit is given by roughly

$$E_b = \frac{A^2}{2} T \tag{8}$$

where A is the baseband signal amplitude (V) and T is the symbol period (sec). The phase variance seen by the tracking loop due to the flat input noise spectrum  $N_{\circ}$  (one-sided) is then given by (see Appendix I)

$$\sigma_{\theta}^{2} \approx \frac{2N_{o}B_{L}}{A^{2}} rad^{2}$$

$$= \left(\frac{B_{L}}{R}\right) \frac{1}{E_{b}/N_{o}} rad^{2}$$

(9)

where the NRZ bit rate is given by  $R=T^{-1}$ . The loop signal to noise ratio,  $\rho$ , is given by

$$\rho - \frac{1}{2\sigma_{\theta}^2} \tag{10}$$

and for a classic second-order phase-locked loop,

$$B_L = \frac{\omega_n}{2} \left( \zeta + \frac{1}{4\zeta} \right) Hz \tag{11}$$

Putting these relationships together, we obtain

$$\rho = \frac{R}{\omega_n} \frac{1}{\left(\zeta + \frac{1}{4\zeta}\right)} \left(\frac{E_b}{N_o}\right) \tag{12}$$

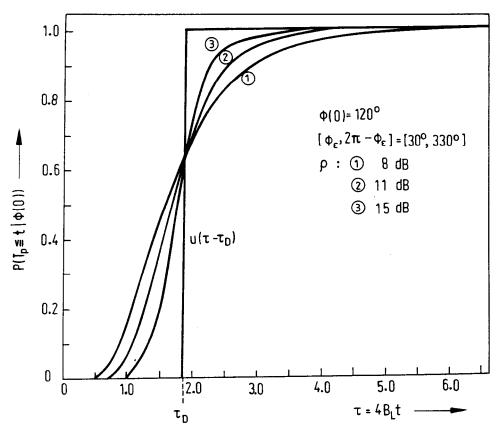

As supported by Figures 8 and 9 from [1], we should have a loop SNR of 15 dB or more for reliable acquisition. A number of researchers argue that capture is not possible for loop SNRs < 6 dB [2-3]. If we take  $\zeta$  as 1.0, for a minimum  $E_b/N_o$  of 6 dB and a loop SNR  $\rho$  of 15 dB, we find from (12) that the loop natural frequency can be at most 1.6 percent of the NRZ data rate. This forces the VCO center frequency accuracy to be a primary design parameter for the entire synchronizer.

Conditional probability of acquiring lock  $P[T_p \le t \mid \phi(0) = 120^\circ]$  (From Heinrich Meyr and Luitjens Popken, Phase Acquisition Statistics for Phase-Locked Loops, *IEEE Transactions on Communications*, Vol. 28, No. 8 © IEEE 1980).

Figure 8.

It is important to note that Figures 8 and 9 assume that the frequency error is zero. In general, the presence of a frequency error greatly detracts from the acquisition performance, lengthening the acquisition time and worst case, preventing acquisition from occuring at all.

From another perspective, the loop may capture the input signal only if the observed phase error during the pull-in process does not exhibit substantial cycle slipping. The criteria may be based upon the total peak phase error due to noise and the application of a step frequency change representing the VCO frequency error with respect to the incoming data rate. Mathematically, this may be expressed as

$$3\sigma_{\theta} + \theta_{p} \le \frac{\pi}{2} \tag{13}$$

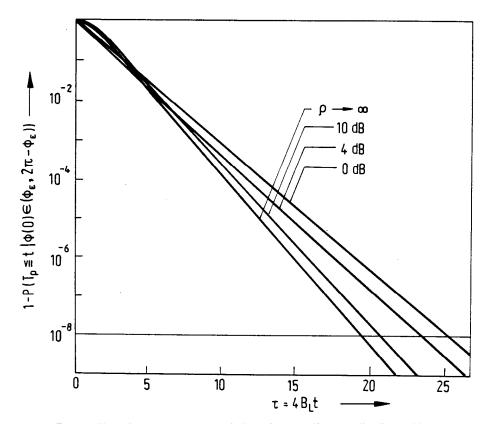

Probability of synchronization failure for a uniformly distributed initial phase error  $\phi(0) \in [\phi_{\varepsilon}, 2\pi - \phi_{\varepsilon}]$  (From Heinrich Meyr and Luitjens Popken, Phase Acquisition Statistics for Phase-Locked Loops, *IEEE Transactions on Communications*, Vol. 28, No. 8 © IEEE 1980).

Figure 9.

where  $\sigma_{\theta}$  is the standard deviation of the phase error due to noise and  $\theta_{p}$  is the peak phase error due to the assumed step frequency error. A three-sigma condition was assumed for the peak value of the additive noise term. From [2] we have for  $\zeta<1$  that

$$\theta_p = \frac{\Delta \omega}{\omega_n} \exp \left[ -\frac{\zeta}{\sqrt{1-\zeta^2}} \tan^{-1} \left( \frac{\sqrt{1-\zeta^2}}{\zeta} \right) \right] rad$$

(14)

and for  $\zeta = 1$ ,

$$\theta_p = \frac{\Delta \omega}{\omega_p} \quad rad \tag{15}$$

Relating  $\Delta\omega$  to the data bit rate R for the 1,0,1... data pattern case, we have that the data rate difference with respect to the nominal rate may be represented by

$$\frac{\Delta\omega}{2\pi} - \frac{\Delta R}{2} \tag{16}$$

If we assume that  $\zeta = 1$ , combining (14), (15), and (16), we obtain the inequality

$$3\sqrt{\frac{5}{4}\pi\left(\frac{f_n}{R}\right)\frac{1}{(E_b/N_o)}} + \left(\frac{\Delta R}{2f_n}\right) \le \frac{\pi}{2}$$

(17)

where  $f_n$  is the loop natural frequency in Hertz. Evaluating (17) for a loop natural frequency of 1.6 percent of R and an  $E_b/N_o$  of 6 dB, the data rate anomoly may be as large as 3.8 percent. Although this is an attractive result, the results indicates nothing about the locking speed which will result. More importantly, the selfnoise of the phase detector due to the random nature of the incoming data has not been included in this discussion, and it is on the order of the incoming white noise term included here or stronger. This would force us to use a smaller loop bandwidth than the present theory would predict for tracking mode which leads to a decrease in the capture range unless the acquisition mode is handled separately.

A number of other factors seriously affect the design if the capture range requirement is excessive. It is quite straight forward to show that the tracking loop must have a bandwidth less

than B/4 Hz in order to be stable. Additionally, the desire to accommodate a transition density range (presently unspecified but probably 30% to 100% for NRZ) results in  $\omega_n$  spanning a range of 1.0 : 1.83 further complicating the stability issue. Large bandwidth tracking loops are also imcompatible with long data run lengths for NRZ signals. (This is obviously not a problem with Manchester signals.) These facts combined with the phase detector self-noise problems alluded to above generally force us to use tracking loop bandwidths which are typically less than one percent of the data rate R.

One solution to the VCO center frequency accuracy problem is of course to use a VCXO for the bit synchronizer VCO. The primary problem here is that the pull range for such oscillators is only at best roughly 0.1 % which is substantially less than the 1 % design requirement presently imposed. A second alternative is to sweep an LC VCO over the frequency range of uncertainty, detect when phase acquisition has in fact occurred, and switch from acquisition mode to tracking mode. This is a popular method which has been used for many years. In the case of a carrier acquisition application, the permissible sweep rate for an acquisition probability of 0.90 is given by [3]

$$R_{90} = 0.5431 \left( 1 - \sqrt{\frac{2}{\rho}} \right) B_L^2 Hz/s$$

(18)

where a damping factor of 0.707 is assumed. The difficulty with this approach in the present context is primarily one of circuit complexity and available real estate. Not only does the additional sweep circuitry need to be included, but means to reliably detect lock and loss of lock must also be provided. If an external controller could assist in the decision making processes, this is an attractive approach to take unless the acquisition speed requirements are excessive. The decision not to use a sweep-type acquisition was based upon the need for i) fairly fast acquisition and ii) the desire that the bit synchronizer be a stand-alone functional module.

Another possible solution is to use a direct digital synthesizer. However, a completely integrated design would be required for the space presently available, and the temperature range would be a problem for presently available devices. Cost would also be fairly high for this approach.

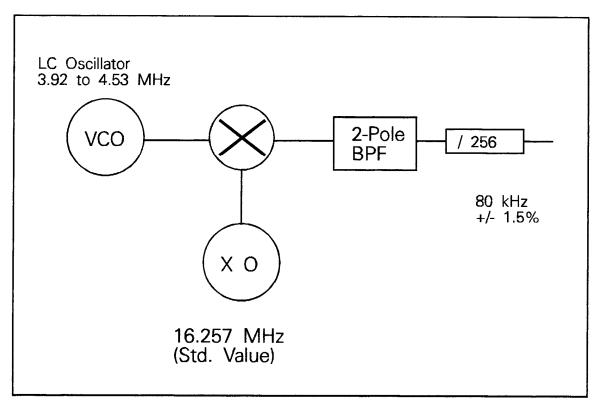

The final oscillator approach which was adopted is shown in Figure 10. It consists of an LC VCO upconverted with a crystal oscillator followed by a divide operation which eases the LC VCO center frequency accuracy and phase noise requirements. As a side note, others have proposed phase-frequency locked methods to accomplish much the same final result [4]. Using this approach, the center frequency accuracy requirements for the LC oscillator are reduced by a factor of 4.8: 1. This frequency plan is well suited

Figure 10 VCO Implementation for Canadair

for the Canadair project, the upconversion and divide operation reducing the LC oscillator phase noise contributions at the output by 62 dB. Although this degree of spectrum cleanup is certainly overkill, Loral dictated that the design be viable for NRZ data rates as high as 2 Mbps where the output divider ratios would of course be substantially smaller. Since this approach provides very good oscillator center frequency accuracy, initial acquisition may be performed by simply using a larger loop bandwidth than that used for the tracking mode. The actual bandwidths paramters chosen will be discussed later.

#### 3.1.2 Phase Noise Requirements

The phase noise requirements of the LC oscillator for the Canadair project are not difficult to meet owing primarily to the large output divider ratio which improves the LC oscillator phase noise spectrum by 48 dB. The theory is developed here nonetheless for follow on applications where this may not be the case.

During steady-state operation, the oscillator phase noise spectrum leads to a random phase error which is equivalent to a random timing error in the clock recovery. The variance of this phase error is given by

$$\sigma_{v}^{2} = \int_{-\infty}^{\infty} S_{\theta}(f) | 1 - H(f) |^{2} df \quad rad^{2}$$

(19)

where  $S_0(f)$  is the oscillator phase noise spectrum and H(f) is the closed-loop transfer function for the tracking loop. The square root of this variance term should be a small quantity, ideally less than 0.02 radians for negligible effect.

The run length issue poses another interesting perspective on the oscillator requirements. During a run of 1's or 0's (NRZ data), since no data transitions are present, the VCO is essentially running open-loop, free to follow its own phase trajectory as it pleases. Obviously, if the phase deviates too far from ideal during the run, the clock recovery may slip an appreciable portion of a symbol leading to poor error performance. This situation is generally dealt with by requiring the VCO excess phase accumulation over the run length to be less than a prescribed quantity which can then be related back to the VCO phase noise spectrum as follows. It can be shown that the variance of the excess phase accumulation over a period of time  $\tau$  (for wide-sense stationary random phase processes) is given by

$$\sigma_{\Delta}^{2}(\tau) - 2[R_{\theta}(0) - R_{\theta}(\tau)]$$

(20)

where  $R_{\theta}$  is the autocorrelation function of the underlying phase noise process. Using the Wiener-Khinchin theorem, this may be expressed in terms of the VCO phase noise spectrum as

$$\sigma_{\Delta}^{2}(\tau) = 8 \int_{0}^{\infty} S_{\theta}(f) \sin^{2}(\pi f \tau) df$$

(21)

where the phase noise spectrum  $S_{\theta}(f)$  was assumed to be symmetric. This may be directly related to the phase noise as measured on a spectrum analyzer as

$$\mathcal{Q}(f) = \frac{1}{2} S_{\theta}(f) \tag{22}$$

Proof of this latter point is given in Appendix II. Assume that the oscillator phase noise spectrum may be modeled by

$$\mathcal{Q}(f) = \frac{K}{\omega^2} \quad rad^2/Hz \tag{23}$$

Substituting this result, we have

$$\sigma_{\Delta}^{2}(\tau) = 16 \int_{0}^{\infty} \mathcal{Q}(f) \sin^{2}(\pi f \tau) df$$

$$= 4K\tau^{2} \int_{0}^{\infty} \frac{\sin^{2}(\pi f \tau)}{(\pi f \tau)^{2}} df$$

$$= 2K\tau \quad rad^{2}$$

(24)

For the 80 kbps NRZ case at hand, the maximum run length is required to be 30 Manchester symbol periods (60 NRZ symbols) making  $\tau$ = 60/80 kHz or 750 microseconds. (Run length is not an issue for bi-phase.) If we require that the oscillator excess phase over this time period have a standard deviation of less than 10 degrees, then K  $\leq$  20.31 implying that the oscillator spectrum at 1 kHz offset must be less than -63 dBc/Hz.

# 3.2 Transition-Tracking Phase Detectors

The phase detector portion of the bit synchronizer is responsible for estimating the timing error between the local clock and that of the incoming noise corrupted data stream. A rigorous study of this area can be quite involved, generally involving subjects such as cyclostationary processes. We will avoid such discussions here, but [6-17] are provided as reference.

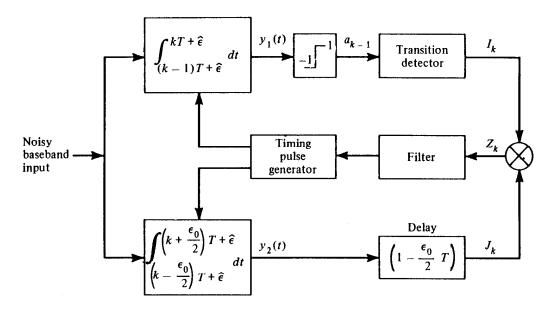

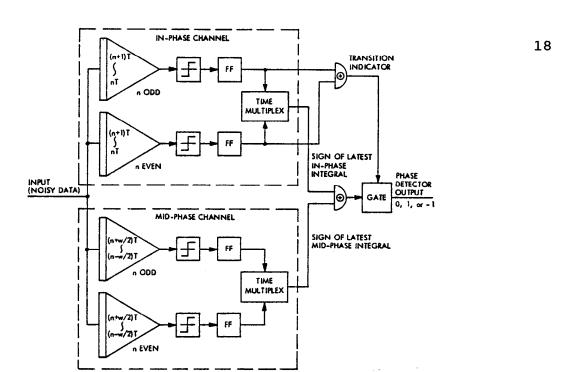

Many factors lead me to take the digital transition tracking method [18] as the baseline concept for the Canadair project. In the present context, this detector results in an unbiased phase error estimate with no self-noise in the limiting case. One form of this type of bit synchronizer is shown here in Figure 11.

Block diagram of an in-phase/midphase symbol synchronizer.

Figure 11. Transition-tracking bit synchronizer from [21].

A close-up of the phase detector concept used in this configuration (with hard-limited output) is shown in Figure 12. The hard-limiting, although simplifing the hardware, results in substantial phase detector self-noise which cannot be neglected in the design analysis. The synchronizer discussed in [18] used a maximum loop bandwidth of only 0.2%.

Figure 12. Phase detector details pertaining to Figure 11 [18].

One of the most simple phase detector types is the classic early-late gate type. The primary problem with this type of phase detector is that the phase detector self-noise is substantial, limiting us to loop bandwidths substantially less that one percent of the NRZ data rate. This limitation would primarily manifest itself as reduced acquisition speed in the Canadair project. Assuming random data, the spectral density of the self-noise may be derived as follows.

For a locked tracking loop in the absence of noise, the phase detector error output may be modeled as

$$\theta_e(t) - \sum_{n=-\infty}^{\infty} a_n \, rect(t-nT) \tag{25}$$

where the  $a_n$  are independent random variables taking values of  $\pm 2\pi$  equally likely. The autocorrelation function is given by

$$R_{\theta_{\alpha}}(\tau) - 4 \pi^2 \bigwedge (\tau) \tag{26}$$

where

The one-sided power spectral density may be found to be

$$S_{\theta_s}(f) = \frac{8\pi^2}{R} \frac{\sin^2(\pi f T)}{(\pi f T)^2} \quad rad^2/Hz$$

(28)

Using this result, the tracking error variance due to the self-noise alone is (assuming a small loop bandwidth  $B_{\rm L}$  << 1/2T)

$$\sigma_e^2 \sim \frac{8\pi^2}{R} B_L \qquad rad^2 \tag{29}$$

or

$$\sigma_e \approx 2\pi \sqrt{\frac{2B_L}{R}} \quad rad. \tag{30}$$

Therefore, for a 1% tracking bandwidth,  $\sigma_{\rm e}=50$  degrees rms which is equivalent to a loop SNR of only -1.8 dB. This is clearly nonsense. In order to obtain a loop SNR of 15 dB due to this selfnoise term, the maximum loop bandwidth may be at most 0.02% which is clearly very small.

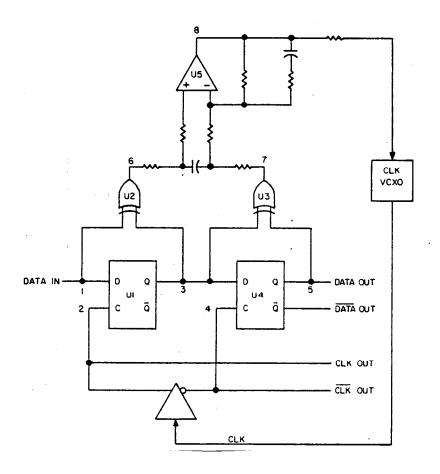

A much simpler phase detector design which has been proposed based upon the transition tracking concept is developed in [19]. Although a <u>patent is pending (or by now awarded)</u> on the method, it leads to substantial circuit simplification which is well worth any minor royalty charges which may be involved. This detector concept (without any matched filter) is shown in Figure 12.

Figure 12. Hogge NRZ bit synchronizer concept [19].

As pointed out in [20], the Hogge method is not completely free of phase detector self-noise due to the  $\pi$  phase difference between the signals at nodes 6 and 7 in Figure 12. This situation may be improved as discussed in [20]. Nonetheless, we will take the Hogge method as our baseline since Hogge is with a domestic firm.

From [20], the power spectral density of the phase error signal in the Hogge method (no noise or ISI) is given by

$$S_e(\omega) = 4\pi^2 T \left| sinc\left(\frac{\omega T}{4\pi}\right) \right|^2 \left| sin\left(\frac{\omega T}{4}\right) \right|^2$$

(31)

for random data. We will use this result in the detailed design portion of this memo in the next section.

# 3.3 Loop Filter and Loop Parameters

In this next section, we will identify the tracking loop parameters needed for the Canadair bit synchronizer. From there, it will be fairly straight-forward to back out what kind of acquisition performance we can obtain prior to entering tracking mode.

The primary requirements in the tracking mode are i) to achieve less than 0.5 % rms clock jitter at 12 dB  $E_b/N_o$  and ii) have a run length capability exceeding 30 symbols. Again, the run length is immaterial for the Manchester waveform.

The tracking loop parameters may be identified as follows. Assuming that the phase detector gain is given by  $K_{do}$  volts/radian for an alternating 1,0,1... NRZ data pattern (100% transition density), the effective phase detector gain with random data present is given by

$$K_d - K_{do} \eta \tag{32}$$

where  $\eta$  is the data stream average transition density. Assuming that the VCO tuning sensitivity is given by  $K_\nu$  rad/s/V and a classic type-2 control loop, the open-loop gain is given by

$$G_{OL}(s) = \frac{K_d K_v}{s} \frac{1 + s\tau_2}{s \tau_1}$$

$$= \omega_n^2 \frac{1 + 2\zeta s/\omega_n}{s^2}$$

(33)

where

$$\omega_{n} - \sqrt{\frac{K_{d} K_{v}}{\tau_{1}}}$$

$$\zeta = \frac{1}{2} \omega_{n} \tau_{2}$$

(34)

The closed-loop transfer function is the classic result

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{\omega_n^2 \left(1 + 2\zeta s/\omega_n\right)}{s^2 + 2\zeta \omega_n s + \omega_n^2} \tag{35}$$

The primary noise contributors to the tracking jitter are

- ISI noise which is assumed to be negligible,

- 2) additive Gaussian noise,

- 3) VCO self-noise

- 4) phase detector self-noise (data-dependent)

The planned VCO approach will have very low self-noise therefore leaving items (2) and (4) as the primary jitter contributors which must be addressed. As reasoned earlier, the tracking error variance due to the Gaussian noise is given by roughly

$$\sigma_n^2 = \frac{B_L}{R} \frac{1}{E_b/N_o} \quad rad^2 \tag{36}$$

The (one-sided) noise power spectral density of the datadependent self-noise was given earlier in (31) as

$$S_e(f) = \frac{4\pi^2}{R} \frac{\sin^2(\pi f T/2)}{(\pi f T/2)^2} \sin^2(\pi f T/2) rad^2/Hz$$

(37)

The tracking error variance due to this contribution is then given by

$$\sigma^{2} = \frac{4\pi^{2}}{R} \int_{0}^{\infty} \frac{\sin^{2}(\pi f T/2)}{(\pi f T/2)^{2}} \sin^{2}(\pi f T/2) |H(f)|^{2} df$$

(38)

For very small loop bandwidths compared to the data rate, this may be approximated as

$$\sigma^2 \sim \frac{4\pi^2}{R} \int_0^{\alpha B_L} \left(\frac{\pi f T}{2}\right)^2 df \quad rad^2$$

(39)

which may be further simplified to

$$\sigma^2 = \frac{\pi^4}{3} \left( \frac{\alpha B_L}{R} \right)^3 \quad rad^2 \tag{40}$$

where  $\alpha$  B<sub>L</sub> is the assumed extent of the pattern noise within the tracking loop. The parameter  $\alpha$  depends upon additional filtering within the control loop beyond that normally found in an ideal type-2 system. Combining (36) and (40), we find the total track variance to be given by

$$\sigma_T^2 - \left(\frac{B_L}{R}\right) \frac{1}{E_b/N_0} + \frac{\pi^4}{3} \left(\frac{4B_L}{R}\right)^3 rad^2$$

(41)

where an  $\alpha$  of 4 was adopted. This result may be used to examine some typical parameter choices as shown below in Table III.

Table III Track Variance Versus Loop SNR

| B <sub>L</sub> /R | $E_b/N_o$ , dB | $\sigma_{\scriptscriptstyle \mathrm{T}}^{\scriptscriptstyle 2}$ , rad <sup>2</sup> | RMS Jitter, % |

|-------------------|----------------|------------------------------------------------------------------------------------|---------------|

| 0.01              | 12             | 0.00271                                                                            | 0.828         |

|                   | 14             | 0.00248                                                                            | 0.792         |

|                   | 16             | 0.00233                                                                            | 0.768         |

Note: These values are different than the original writeup because a slightly different  $E_b/N_o$  relationship was used, and upon my own derivation of (37) it was found that the original reference was for a one-sided spectrum rather than a two-sided spectrum as I initially assumed.

The phase detector self-noise term is appreciable in setting the loop SNR as evidenced in Table III. This term was evaluated separately for a number of parameter choices as shown in Table IV.

Table IV Tracking Jitter Due to Phase Detector Self-Noise

| RMS Jitter, %     |      |      |       |  |  |

|-------------------|------|------|-------|--|--|

| B <sub>L</sub> /R | α= 2 | α= 3 | α= 4  |  |  |

| 0.001             |      |      | 0.023 |  |  |

| 0.005             |      |      | 0.26  |  |  |

| 0.01              |      | 0.47 | 0.73  |  |  |

| 0.015             | 0.47 | 0.86 | 1.33  |  |  |

| 0.013             | 0.73 | 1.33 | 2.05  |  |  |

| 0.03              | 1.33 | 2.45 | 3.77  |  |  |

| 0.04              | 2.05 | 3.77 | 5.81  |  |  |

| 0.05              | 2.87 | 5.27 | 8.11  |  |  |

Note: Values differ from original writeup. See note, Table III.

Similarly, the jitter due to the additive Gaussian noise term may be evaluated as shown in Table V.

Table V Tracking Jitter Due to Additive Noise

| B <sub>L</sub> /R | $E_b/N_o=$ | Jitter, %<br>6 dB | RMS<br>10 dB | 12 dB |

|-------------------|------------|-------------------|--------------|-------|

| 0.002             |            | <br>0.36          | 0.23         | 0.18  |

| 0.002             |            | 0.56              | 0.36         | 0.28  |

| 0.01              |            | 0.80              | 0.50         | 0.40  |

| 0.015             |            | 0.98              | 0.62         | 0.49  |

| 0.02              |            | 1.13              | 0.71         | 0.57  |

The Gaussian variance contribution to the tracking error is fairly small compared to the self-noise contribution shown in Table IV, largely because the Gaussian noise spectrum is white whereas the self-noise spectrum is not. The primary motivation for reducing the loop bandwidth between acquisition and tracking modes is then to reduce the phase detector self-noise contribution to the tracking error variance.

From (32) and (34), the damping factor is a function of the transition density as given by

$$\zeta = \frac{1}{2} \sqrt{\frac{K_{do} \eta K_v}{\tau_1}} \tau_2$$

$$= \zeta_o \sqrt{\eta}$$

(42)

where  $\zeta_{\circ}$  is the damping factor for a transition density of 100%. Therefore, a change in  $\eta$  from 30% to 100% results in a damping factor change of 1 to 1.83. The loop bandwidth changes similarly as given by

$$B_L = \frac{\omega_{no}}{2} \left( \zeta_o \eta + \frac{1}{4\zeta_o} \right)$$

(43)

which results in a bandwidth range of 1.0 to 2.27. The parameter spread for Manchester signaling will of course be smaller since the minimum transition density in this case is 50%.

Based upon this information, a  $B_L$  of 0.005 was selected for the tracking mode in order to obtain adequately low clock jitter performance (See Table IV and V). In order to accommodate the range of transition densities expected,  $\zeta_o$  was chosen to be 1.0 since this would result in a  $\zeta$  of 0.55 for the minimum transition density. (For a given  $\omega_n$ , a damping factor of 0.5 results in the minimum noise bandwidth for a classic second-order system.) This is also an adequate amount of damping to provide reasonable transient performance.

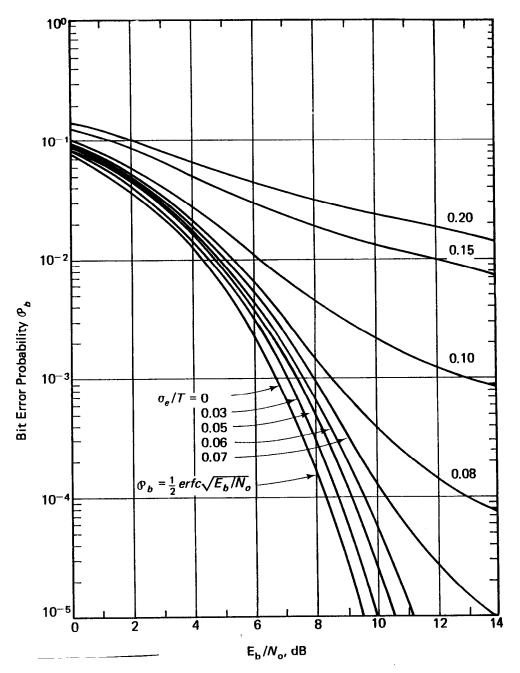

To some degree, discussion of loop parameters for acquisition is less clear because it is a stochastic process which is difficult to analyze except by simulation. The loop parameters selected for acquisition were chosen based upon i) the need to keep the ratio of parameters between acquisition and tracking modes reasonable so as not to loose lock when switching between acquisition and tracking modes, and ii) upon the rule of thumb to keep the associated rms jitter less than roughly 3%. This latter requirement was based upon the BER curves shown in Figure 14 where the 3% value results in negligible departure from theory. This is admittedly a very conservative position, and one which could be challenged. This rationale led to an acquisition bandwidth selection for B<sub>L</sub>/R of 0.02. The damping factor choice for the acquisition mode was the same made for the tracking mode.

The forementioned bandwidths result in an acquisition to tracking loop bandwidth ratio of 4. This may seem small, but this requires for instance a 16:1 change in the loop  $\tau_1$ . Larger ratios could of course be considered for faster acquisition performance, but not without an increased risk of loosing lock while handing off to the tracking mode. The adopted 4:1 ratio represented about the maximum ratio beyond which much more exhaustive analysis and simulation would be required to confirm performance. Based upon Figure 8, if the transition density is 100%, the data rate error zero, and the loop SNR > 15 dB, reliable synchronization should be achieved in t  $\leq$  (B<sub>L</sub>)<sup>-1</sup> seconds which for NRZ symbols translates to 50 symbols. Based upon the available data (Appendix III), this is quite optimistic when random data is present, and a finite data rate error exists. Characterizing of the initial synchronization

Average probability of bit error versus  $E_b/N_0$  with standard deviation of the symbol sync error  $\sigma_{\epsilon}$  as a parameter (NRZ) [From Lindsey and Simon, 1973, 469, Fig. 9-37]

Figure 14.

statistics remains an area where additional evaluation would be valuable. Circuit implementation details are left to section 4.0.

# 3.4 Matched Filter Selection

Although the discussion of the bit synchronizer input filtering appears somewhat late in this discussion, it was in fact the first area that was analyzed during the design process. The principal reason for analyzing the matched filter performance first was that if the transmit premodulation filter had been chosen improperly, substantial intersymbol interference can result which degrades both the bit error rate performance due to eye closure as well as increasing the jitter on the recovered clock. Selection of the matched filter is a primary systems-level consideration which could have potentially involved the transmitter design also, so it only made sense to eliminate this possible problem as early as possible.

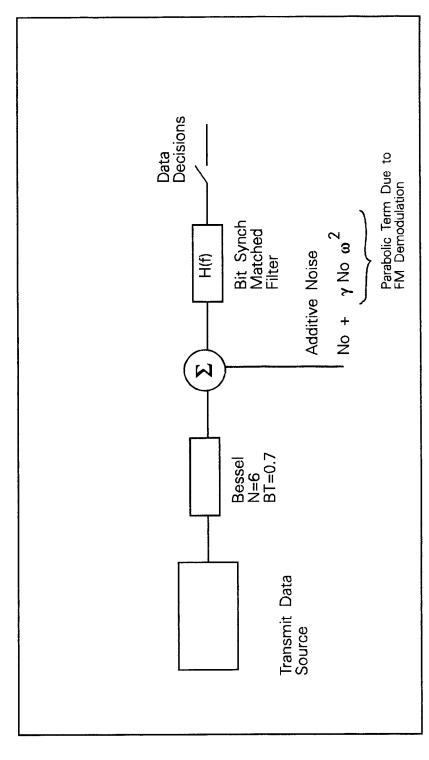

### 3.4.1 NRZ Matched Filter Selection

A simplified block diagram of the design situation for Canadair is shown in Figure 15. The FM subcarrier link is assumed to be transparent even though the input noise spectrum to the bit synchronizer will be parabolic rather than white as a result. In general, the complete analysis was carried on assuming that the synchronizer was baseband in nature. This was necessary since much of the needed information was unavailable to proceed otherwise and it led to significant simplification in the analysis/design effort.

It can be shown that the bit error probability for the system shown in Figure 15 can be computed as

$$P_{e} = \frac{1}{2} - \frac{1}{\pi} \int_{0}^{\infty} \frac{\sin[\omega p(t_{o})]}{\omega} e^{-\frac{1}{2}\sigma^{2}\omega^{2}} C(\omega) d\omega$$

(44)

where

$$C(\omega) = \prod_{e=-L; \neq 0}^{L} \cos[\omega p(t_o + e T)]$$

(45)

Analysis Model for Bit Synchronizer Matched Filter Optimization. Figure 15.

$$\sigma^2 = \int_{-\infty}^{\infty} \frac{N_o}{2} \left( 1 + \gamma 4 \pi^2 f^2 \right) |H(f)|^2 df$$

(46)

and

- t. Time corresponding to the received matched filter output peak

- T Symbol period, s

- L Number of adjacent symbols over which intersymbol interference is significant

A number of other approaches may be used to compute the bit-error probability but this is the approach used in the analysis software which I have written.

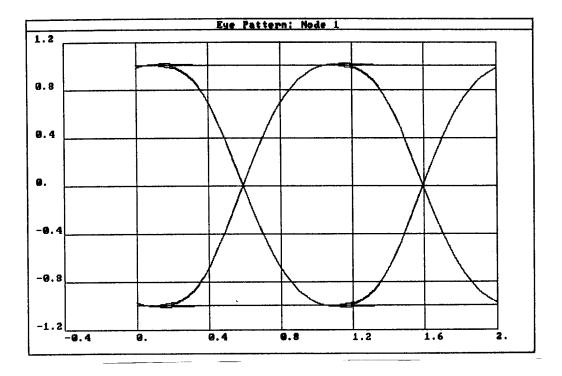

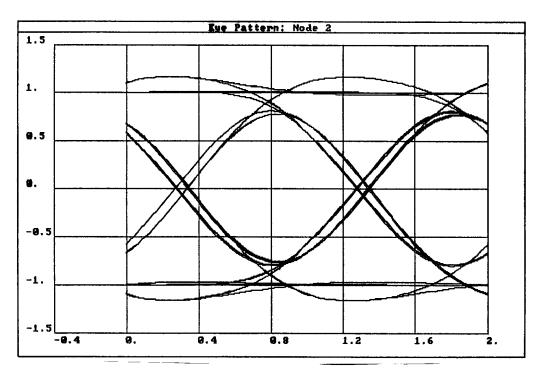

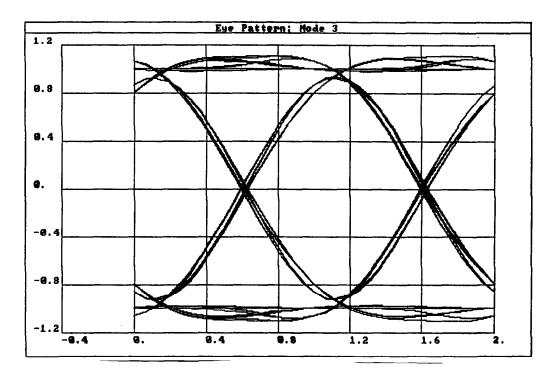

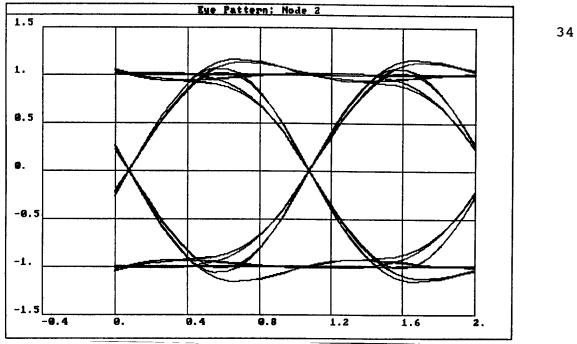

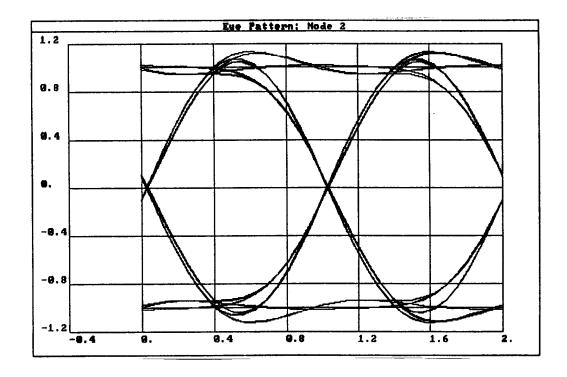

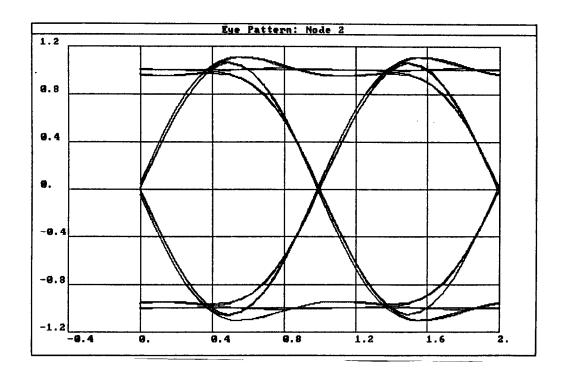

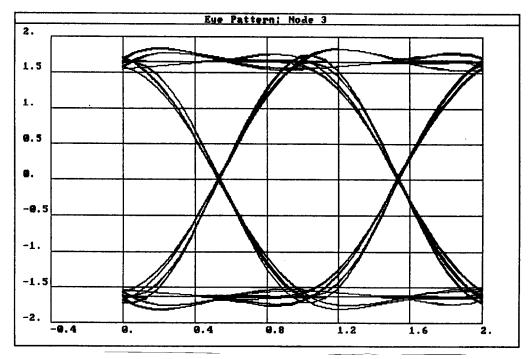

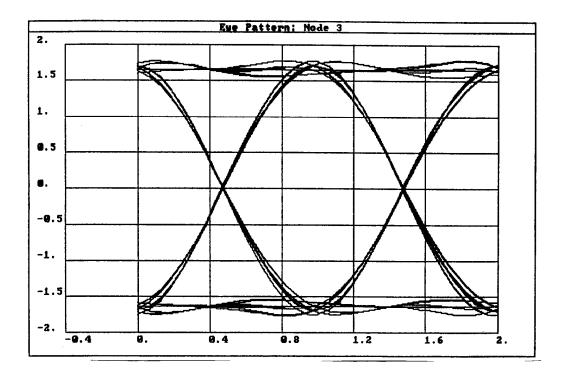

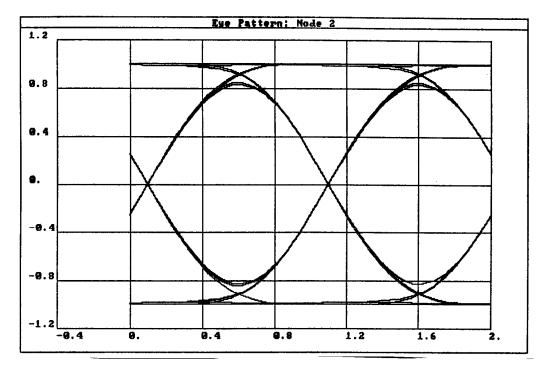

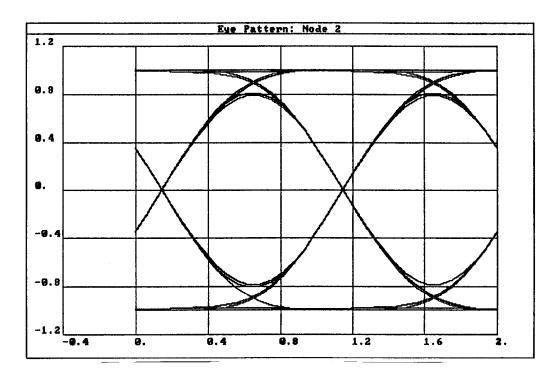

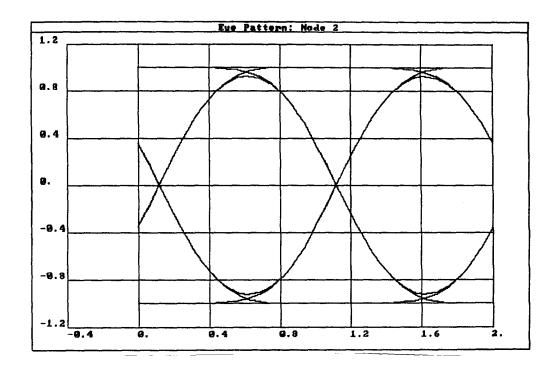

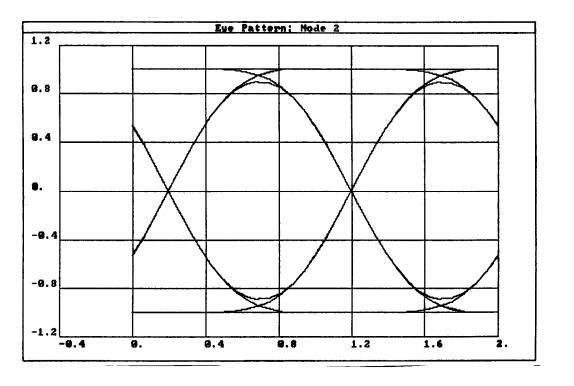

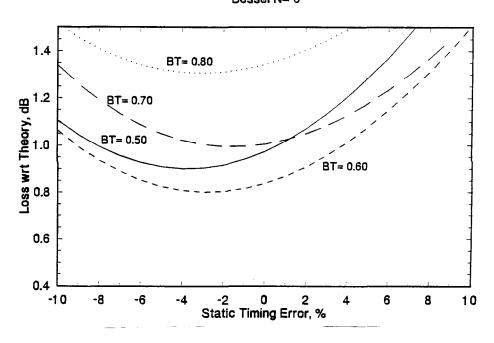

The data eye pattern immediately following the transmit filter  $H_{\scriptscriptstyle T}(f)$  is shown in Figure 16. The constant group delay of the Bessel filter is clearly evident in that all of the signal trajectories are tight. Just arbitrarily selecting an N=3 Butterworth filter with BT= 0.5 for the bit synchronizer matched filter leads to the poor output eye pattern shown in Figure 17. Clearly, this haphazard choice would lead to substantial intersymbol interference (ISI).

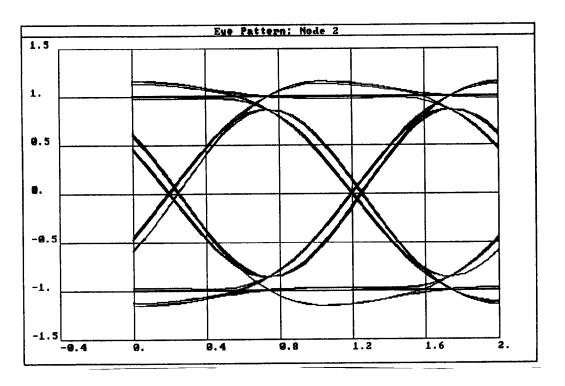

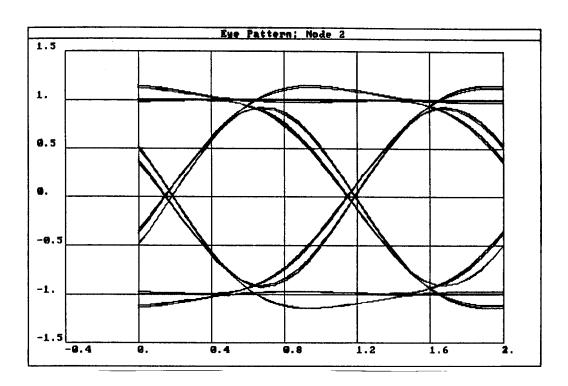

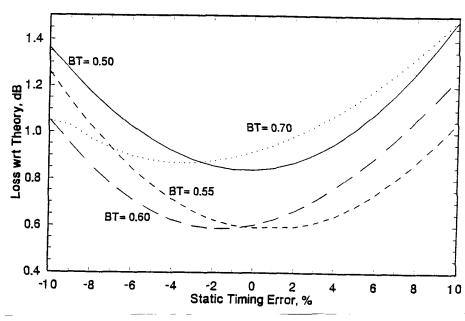

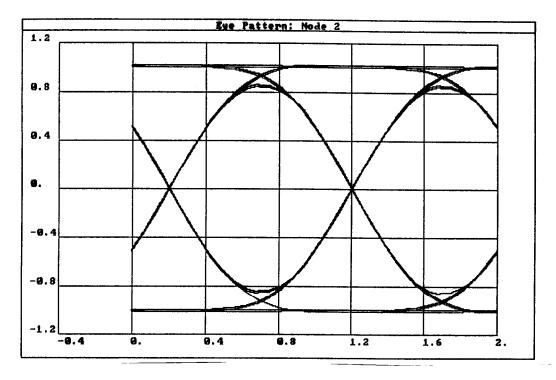

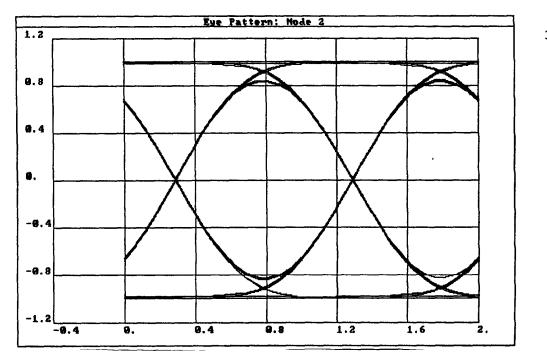

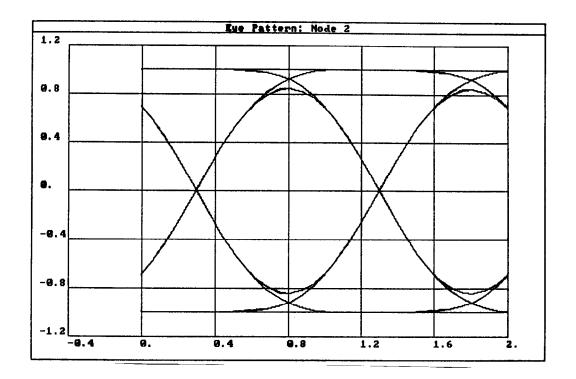

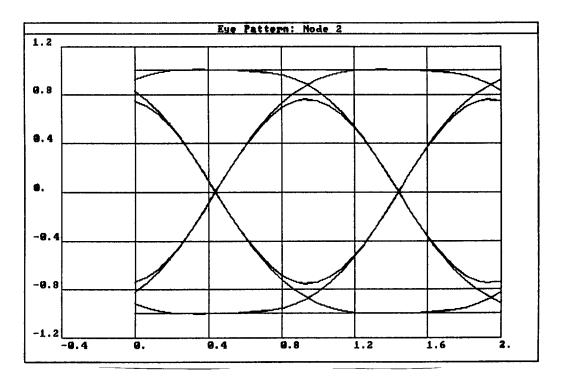

In order to find a suitable matched filter for the bit synchronizer, the N=3 Butterworth and N=3 Chebyshev (0.1 dB ripple) families were initially considered for an acceptable solution since these filters were representative of the minimum useful complexity. The search was widened to a number of other filter types and these results are documented in the next several figures. In the end, an N=6 Bessel filter with BT= 0.6 was selected for the matched filter function. Once in PWB layout however, it was clear that the circuit density was going to be extreme, so an N=4 Bessel was actually implemented instead in order to reduce the parts count.

Once the bit synchronizer is integrated with the remaining elements of the Canadair system, the impact of the nonwhite noise spectrum (arising from the FM subcarrier demodulation) may become apparent, and tightening the matched filter bandwidth may be desirable. Again, if more information had been available at the outset, these factors could have been included in the original analysis. Since the noise spectrum will be an increasing function of frequency, it is important that the matched filter have an ultimate attenuation roll off which exceeds 20 dB per decade. Otherwise, the sample variance at the data decision point in the synchronizer will be unbounded. This condition is easily satisfied with the N=4 Bessel filter presently being used.

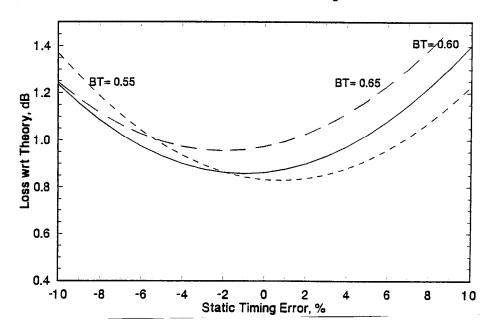

Additional plots are included in the next figures which show the performance degradation with respect to theory for the bit synchronizer as a function of static timing error in the clock recovery. These plots are valuable for quickly assessing the impact of finite recovered clock jitter upon the actual matched filter mismatch loss. In lieu of having detailed information about the recovered clock jitter, normally the tracking error probability distribution is well approximated by the Tikhonov density which is given by

$$p(\theta) = \frac{e^{\rho \cos(\theta)}}{2\pi I_0(\rho)}$$

(47)

where  $\boldsymbol{\rho}$  is the tracking loop SNR. The closed-loop system bit error probability can then be calculated as

$$P_{e} = \int_{-\pi}^{\pi} P_{s}(\theta) p(\theta) d\theta$$

(48)

and  $P_s(\theta)$  is the probability of bit error given a static timing error of  $\theta$  radians. This was precisely the procedure used in obtaining Figure 14.

Summarizing this section, the matched filter losses for the Canadair system (assuming a white noise spectrum out of the subcarrier demodulator) should be less than 1.0 dB based upon the results shown in Figure 38. Since the recovered clock jitter is being designed to be very small, losses relating to clock jitter should be negligible.

# 3.4.2 Mismatch Loss for Manchester Symbols

As stated earlier, originally Canadair was planning to use NRZ-L for the data link and this decision was later changed to Manchester. Use of the NRZ matched filter for receiving Manchester symbols leads to a 3 dB loss with respect to theory as we will now demonstrate. This loss could be almost completely avoided by going to 3-bit soft decisioning on the data decisions, but Loral chose not to incorporate this performance enhancement.

Assuming square NRZ symbols at the bit synchronizer input, the bit error rate is given by

$$P_{NRZ} = \frac{1}{2} \operatorname{erfc} \left( \sqrt{\frac{E_s}{N_o}} \right) \tag{49}$$

where  $E_s$  is the energy per NRZ symbol and  $N_o$  is the one-sided noise power spectral density in watts/Hertz. In the Manchester symbol case, separate decisions are made on the first half and the second half of the symbol, treating each as an NRZ symbol. For Canadair, only the first half will be used to estimate the true data bit, and since this effectively results in throwing away half of the energy per symbol available, clearly, the loss must be 3 dB. Performing decisioning on the second half of the symbol leads to negligible improvement so the system is in fact left with a 3 dB performance loss.

Assuming that decisions are made on both halves of the Manchester symbol, further assume that the following decision rule has been adopted:

Clearly the decision table entries for the "11" and "00" cases could be reversed, but this has no impact in the end. The probability of a Manchester symbol error is then

$$P_{se} = p_1 (p_{01|1} + p_{00|1}) + p_0 (p_{10|0} + p_{11|0})$$

where

| $\mathbf{p_1}$      | Probability of sending a data 1                |

|---------------------|------------------------------------------------|

| p <sub>o</sub>      | Probability of sending a data 0                |

| $p_{01 1}$          | Probability of receiving a 01 NRZ pattern when |

| 2 02 12             | sending a data 1 Manchester symbol             |

| $\mathbf{p}_{00 1}$ | Probability of receiving a 00 NRZ pattern when |

| 1 00/1              | sending a data 1 Manchester symbol             |

| $p_{10 0}$          | Probability of receiving a 10 NRZ pattern when |

| 1-1010              | sending a data 0 Manchester symbol             |

| $\mathbf{p}_{11 0}$ | Probability of receiving a 11 NRZ pattern when |

| L'III               | sending a data 0 Manchester symbol             |

Assuming random 1 and 0 data symbols, the Manchester symbol error probability is given by

$$P_{se} = \frac{1}{2} \left( p_b^2 + p_b (1 - p_b) \right) + \frac{1}{2} \left( p_b^2 + p_b (1 - p_b) \right)$$

$$= p_b^2 + p_b (1 - p_b)$$

$$\approx p_b (1 - p_b) \approx p_b$$

(50)

Figure 16. Eye diagram at the transmitter premodulation filter output.

Figure 17. Recovered eye pattern at the bit synchronizer matched filter output for an N=3 Butterworth BT= 0.5 filter selection.

Figure 18. Bit synchronizer eye pattern for an N=3 Butterworth BT= 0.55 matched filter.

Figure 19. Bit synchronizer eye pattern for an N=3 Butterworth BT= 0.60 matched filter.

Figure 20. Bit synchronizer output eye pattern for an N=3 Butterworth BT= 0.60 matched filter with first order delay equalizer (equalizer BT=0.62).

Figure 21. Bit synchronizer matched filter losses for the N=3 Butterworth family as a function of static clock recovery timing error.

James A. Crawford R&D December 1990

Bit synchronizer eye pattern for an N=3 Chebyshev 0.1 dB ripple BT= 0.55 matched Figure 22. filter.

Bit synchronizer eye pattern for an N=3 Chebyshev 0.1 dB ripple BT= 0.60 matched Figure 23. filter.

Figure 24. Bit synchronizer eye pattern for an N=3 Chebyshev 0.1 dB ripple BT= 0.65 matched filter.

Figure 25. Bit synchronizer eye pattern for an N=3 Chebyshev 0.1 dB ripple BT= 0.50 matched filter with a first-order delay equalizer (equalizer BT=0.7).

Figure 26. Bit synchronizer eye pattern for an N=3 Chebyshev 0.1 dB ripple BT= 0.55 matched filter with a first-order delay equalizer (equalizer BT=0.7).

Figure 27. Bit synchronizer eye pattern for an N=3 Chebyshev 0.1 dB ripple BT= 0.65 matched filter with a first-order delay equalizer (equalizer BT=1.0).

Figure 28. Bit synchronizer eye pattern for an N=3 0.5 degree Linear Phase BT= 0.60 matched filter.

Figure 29. Bit synchronizer eye pattern for an N=3 0.5 degree Linear Phase BT= 0.55 matched filter.

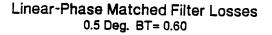

Figure 30. Bit synchronizer matched filter losses for the N=3 Linear Phase (0.5 Deg) family as a function of static clock recovery timing error.

Figure 31. Bit synchronizer eye pattern for an N=4 0.5 degree Linear Phase BT= 0.60 matched filter.

Figure 32. Bit synchronizer eye pattern for an N=5 0.5 degree Linear Phase BT= 0.60 matched filter.

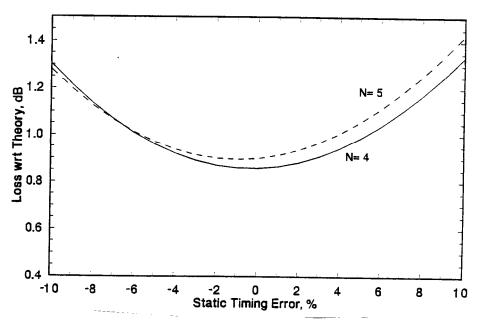

Figure 33. Bit synchronizer eye pattern for an N=6 Bessel BT= 0.80 matched filter.

Figure 34. Bit synchronizer eye pattern for an N=6 Bessel BT= 0.70 matched filter.

Figure 35. Bit synchronizer eye pattern for an N=6 Bessel BT= 0.60 matched filter.

Figure 36. Bit synchronizer eye pattern for an N=6 Bessel BT= 0.50 matched filter.

Figure 37. Bit synchronizer matched filter losses for the N=4 and N=5 Linear Phase (0.5 Deg) BT=0.60 filters as a function of static clock recovery timing error.

Figure 38. Bit synchronizer matched filter losses for the N=6 Bessel family as a function of static clock recovery timing error.

where  $p_b$  is the probability of an NRZ symbol (half Manchester symbol) being received in error. Although looking at both NRZ halves will help slightly at very poor  $p_b$ , in general, the bit error rate is simply that of the NRZ symbol stream implying once again a 3 dB impact to the synchronizer performance with respect to theory.

#### 3.5 Lock Detection

The lock detection indicator is intended to be used to

- 1) indicate the lock/unlock condition to external devices

(if present)

- 2) cause the synchronizer to switch from acquisition mode (wide bandwidth) to tracking mode (narrow bandwidth).

Because the switching action from acquisition to tracking mode is automatic, some hysteresis is required in the circuitry in order to guarantee smooth operation. As presented in Figure 39, the lock detector used in the Canadair bit synchronizer is based upon the following principles:

- the number of observed legal bit transitions when averaged over a given time period must be greater than some value  $\gamma_{\rm T}$ . The output from the lower filter in Figure 39 is proportional to the number of the valid bit transitions occuring over a time period which is given by roughly  $\tau=RC$ ,

- the number of illegal bit transitions when averaged over a given time period must be greater than some value  $\gamma_r$ . The output from the upper filter in Figure 39 is proportional to the number of the illegal bit transitions occuring over a time period which is given by roughly  $\tau=RC$ .

Ideally,  $\gamma_{\text{T}}$ ,  $\gamma_{\text{F}}$ , and the two time constants are chosen to meet specified detection and false alarm probabilities. In order to simplify the analysis involved, we will focus on the 100% transition density case which is nearly equivalent to considering a sine wave in additive Gaussian noise at the matched filter output. Use of the number of legal bit transitions in a specified time interval is an insufficient indicator of synchronizer lock as we will now explore briefly. The observed signal at the bit synchronizer input may be represented by

$$x(t) = a\cos(\omega_0 t) + b\sin(\omega_0 t) + n(t)$$

(51)

V1: Illegal Transition Detector V2: Legal Transition Detector

Figure 39. Lock Detector Methodology for Canadair.

where a and b are independent mean-zero random Gaussian constants of variance  $\sigma^2$  and n(t) is white Gaussian noise with spectral density  $S_o$ . The probability of a zero-crossing in the interval  $(t,t+\tau)$  given an ideal lowpass filter with cutoff frequency  $\omega_c$  (for the matched filter) is given by

$$p(\tau) = \frac{1}{\pi} \sqrt{\frac{\pi \omega_o^2 \sigma^2 + S_o \omega_c^3 / 3}{\pi \sigma^2 + S_o \omega_c}}$$

(52)

For the noise-only case,

$$p_n(\tau) = \frac{1}{\pi} \frac{\omega_c}{\sqrt{3}} \approx f_c 1.15$$

(53)

On the other hand, for a 1,0,1,... data pattern with no noise, the probability of a zero crossing in the interval  $(t,t+\tau)$  is

$$p_s(\tau) = \frac{1}{\pi} \frac{2\pi f_c}{2} = f_c \tag{54}$$

where a matched filter BT=0.5 was assumed. Since the ratio of  $p_s$  to  $p_n$  only varies from 1.0 to 1.15 over all possible signal to noise ratios, clearly the number of zero-crossings per unit time results at best in a very poor lock statistic. If the SNR is very high, the number of zero-crossings per unit time could be used to indicate an insufficient transition density on the incoming data stream, but this is rarely needed if a proper system design has been performed.

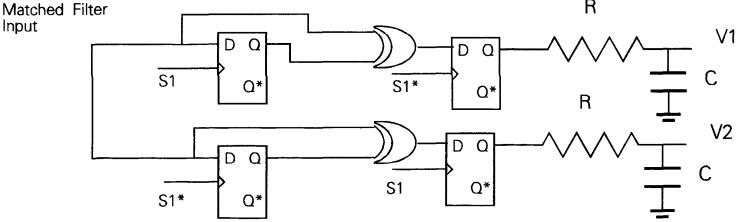

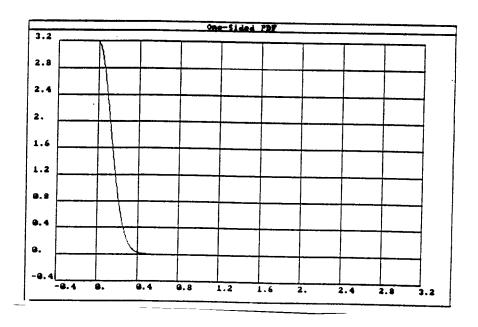

One of the most robust indicators of lock integrity is the location of the zero-crossings in time with respect to a fixed clock whose frequency is set to the nominal data rate. The probability density for the instantaneous phase of a sine wave immersed in additive white Gaussian noise is given by

$$p(\theta) = \frac{1}{2\pi} e^{-\rho} \left[ 1 + \sqrt{2\rho} e^{\rho \cos^2(\theta)} \cos(\theta) \psi(A, \theta, \sigma) \right]$$

(55)

where

$$\psi(A, \theta, \sigma) = \int_{-\frac{A\cos(\theta)}{\sigma}}^{\infty} e^{-u^2/2} du$$

$$\frac{A}{\sigma} = \sqrt{2\rho}$$

(56)

- A sine wave amplitude

- $\sigma^2$  noise variance

- ρ signal-to-noise ratio

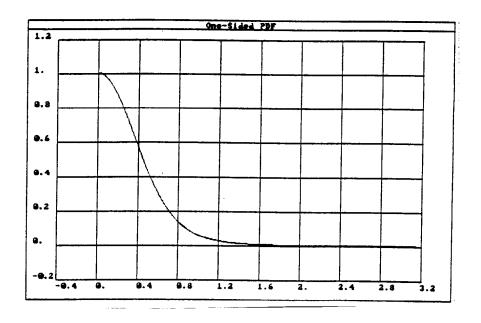

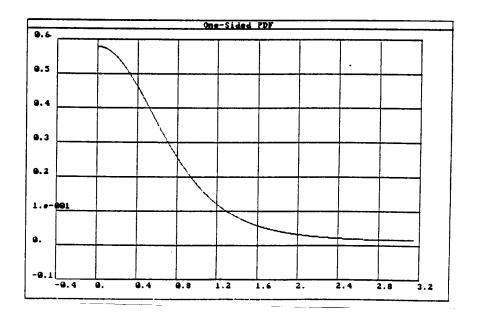

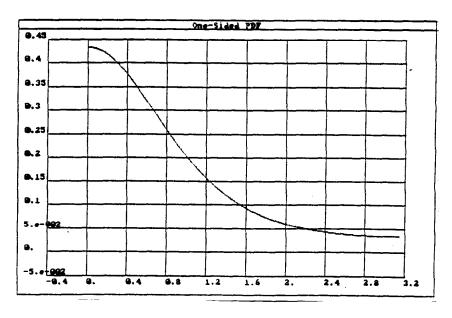

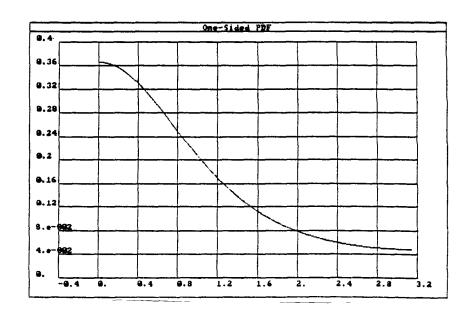

Several plots of  $p(\theta)$  versus  $\rho$  are provided in Figures 40 through 45. As the signal-to-noise ratio becomes small,  $p(\theta)$  tends toward the uniform probability density function as we would expect. From Figures 40 through 42 it is obvious that the zero crossings are tightly held to their nominal noise-free location (at zero radians) which is what we need for a reliable lock indicator function.

For best response time, the smoothing time constants would be selected differently for the acquisition and tracking modes. However, in the interest of saving board space, this was not done since we are only required to operate at fairly good  $E_{\rm b}/N_{\rm o}$  values. We note that the smoothing time constants must be at least on the order of several tracking loop time constants in order to prevent the circuitry from construing a saddle-point phase error trajectory as a locked condition.

Obviously, we have that

for every transition. Assuming that the bit synchronizer clock is stationary during the smoothing interval due to the supposed lock condition, a sufficient lock indication can be had as

- E{ Prob[ Valid Crossing | Transition Present ] ) -

- E{ Prob[ Invalid Crossing | Transition Present ] }

where E{} denotes time averaging. If this quantity is greater than a threshold  $\Lambda_o$ , lock has occurred. Using the relationship for the total probability, it suffices to consider

Figure 40.  $p(\theta)$ ,  $\theta$  in radians. SNR= 15 dB.

Figure 41.  $p(\theta)$ ,  $\theta$  in radians. SNR= 10 dB.

Figure 42.  $p(\theta)$ ,  $\theta$  in radians. SNR= 5 dB.

Figure 43.  $p(\theta)$ ,  $\theta$  in radians. SNR= 0 dB.

James A. Crawford R&D December 1990

Figure 44.  $p(\theta)$ ,  $\theta$  in radians. SNR= -3 dB.

Figure 45.  $p(\theta)$ ,  $\theta$  in radians. SNR= -5 dB.

James A. Crawford R&D December 1990

$$E$$

{ Prob( Valid Transition | Transition Present ) }  $\frac{\sum_{lock}^{Lock}}{\langle \frac{1-\Lambda_o}{2} | (57) \rangle}$

The expected probability here can be approximated by an appropriate integral of  $p(\theta)$  given by (55).

If the synchronizer clock is assumed to be properly positioned in the 1,0,1,... eye pattern, the probability of a valid zero-crossing is

$$p_{v} = \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} p(\theta) d\theta \tag{58}$$

where  $p(\theta)$  is given by (55). For the noise-only case, since  $p(\theta)$  becomes uniform, the probability of an illegal transition during each T-second symbol period is simply 0.5. Each symbol period may then be viewed as a discrete event where lock is declared only if Q or more of the last M observed transitions were valid. The probability of properly detecting lock on one block of M transitions is then given by

$$P_{d} = \sum_{i=0}^{M} {M \choose i} p_{v}^{i} (1-p_{v})^{M-i}$$

(59)

For the noise-only case, the probability of erroneously declaring lock is therefore given by

$$P_f = \sum_{i=\varrho}^{M} {M \choose i} \left(\frac{1}{2}\right)^i \tag{60}$$

Since we will be working with fairly large M values, these discrete probabilities (binomial distribution) may be approximated using the DeMoivre-Laplace theorm as

$$\begin{pmatrix} n \\ k \end{pmatrix} p^k q^{n-k} \approx \frac{1}{\sqrt{2\pi npq}} e^{-\frac{(k-np)^2}{2npq}}$$

(61)

James A. Crawford R&D December 1990

Using this theorem, we obtain

$$P_{d} = \frac{1}{2} + erf\left(\frac{-Q + Mp_{v}}{\sqrt{Mp_{v}(1 - p_{v})}}\right)_{Mp_{v} > Q}$$

$$P_{f} = \frac{1}{2} - erf\left(\frac{Q - M/2}{\sqrt{M/4}}\right)$$

where

$$erf(\alpha) = \int_{0}^{\alpha} \frac{e^{-x^{2}/2}}{\sqrt{2\pi}} dx$$

(62)

The false-alarm rate may be roughly approximated (without rigorous justification) by

$$R_f \sim \frac{P_f}{MT}$$

Alarms/sec (63)

As stated earlier, MT must correspond to a number of tracking loop time constants in order to avoid erroneous lock indications due to saddle-points. Assuming that 4 loop time constants is adequate,

$$M \approx \frac{1}{T} \frac{4}{\zeta \omega_n} - \frac{4R}{\zeta \omega_n} \tag{64}$$

In the simple lock detector context (Figure 39), we can consider the simple lowpass filters as having memory length  $\tau=RC$  from which

$$M = \frac{\tau}{T} = \tau R \tag{65}$$

which leads to

$$\tau - \frac{4}{\zeta \omega_n} \tag{66}$$

or finally

$$\tau = 4 \frac{\zeta + 1/4\zeta}{2B_L \zeta}$$

$$= \frac{2}{B_L} \left( 1 + \frac{1}{4\zeta^2} \right)$$

(67)

For the situation at hand,  $B_{\rm L}=0.02$  R,  $\zeta=1.0$ , and R= 80 kbps which gives  $\tau=0.00156$  s or  $f_{\rm c}=102$  Hz. The  $\tau$  used in the final design corresponds to roughly double this value (3 msec) thinking in terms of Manchester symbols rather than NRZ symbols. The value can be easily changed as further measurements warrant by a single resistor change if desired.

NOTE: The 3 ms  $\tau$  value corresponds to 120 Manchester symbols periods. The delay could be shortened at the expense of an increased false alarm rate but this should be a non-issue for the Canadair project.

For a false-alarm rate of less than once per every 24 hours (86,400 seconds), for the noise-only case,

$$P_f \le R_f MT - R_f \tau \implies P_f \le 1.4 \cdot 10^{-7}$$

(68)

From (62), we have

$$P_{f} \approx \frac{e^{-x^{2}/2}}{x\sqrt{2\pi}} |_{x = \frac{Q-M/2}{\sqrt{M/4}}}$$

(69)

leading to  $x \ge 5.2$  or  $Q \ge 308$  for the case where M=500. Hence, if the devices in Figure 39 are CMOS operating from +5 volts, the V2 threshold for comparison would be set at roughly (308/500) 5 = 3.1 volts.

For the probability of proper lock detection, from (62) we have the following results:

| p <sub>v</sub> | ΥΥ     | P <sub>d</sub> |

|----------------|--------|----------------|

| 0.55           | -2.967 | 0.001          |

| 0.60           | -0.73  | 0.24           |

| 0.65           | 1.594  | 0.95           |

| 0.70           | 4.099  | >0.999978      |

| 0.75           | 6.920  | ~1.0           |

| 0.80           | 10.286 | ~1.0           |

Recognizing that  $p_{\nu}$  is given by (58), casual examination of Figures 40 through 42 shows that  $P_d$  at SNRs of 5 dB should be essentially unity. In other words, explicit evaluation of (62) at different SNRs is not required to substantiate the claim that this approach should provide good detection performance.

The foregoing lock detection analysis has made use of a number of assumptions and approximations. The indication of lock can without question be asserted faster if  $\tau$  is shortened as suggested, but careful measurements would be necessary to thoroughly investigate all of the possible ramifications.

# 4.0 Detailed Design Considerations

Time and space do not allow every aspect of the design details to be recorded in this document, but an attempt will be made to identify the most important elements of the design approach. The bit synchronizer signal interface is quite simple and is described below.

Bit Synchronizer Interface Signals (Less Power)

| Inputs:<br>J1-8                     | Analog baseband positive signal input, ±1 volt maximum                                                                                  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| J1-7                                | Analog baseband negative signal input, or signal return (ground), ±1 volt maximum.                                                      |

| Outputs:<br>P1-31<br>P1-60<br>P1-63 | Open-collector lock indication. LOW = Locked<br>Bit synchronizer recovered clock, 80 kHz, CMOS<br>Bit synchronizer recovered data, CMOS |

### 4.1 Matched Filter

The matched filter design is an N=4 Bessel with BT= 0.60. This was adopted rather than the N=6 Bessel in order to conserve board real estate. Device U1 functions as a unity-gain differential or single-ended buffer amplifier. The OP-42 is compensated internally for unity gain stability. In the case of a 1,0,1,... NRZ data pattern at 2 Mbps, under bandlimited conditions, the maximum input slew rate is

$$S_{\text{max}} = \omega V_{p} \tag{70}$$

where  $V_p$  is the peak signal swing. If the input signal amplitude is limited to 1 volt peak, the maximum slew rate is approximately 6.28 volts/usec. This leaves substantial margin compared to the Op-42E slew rate capability which is roughly 50 V/usec at 25 C. Decoupling capacitors of 0.1 uF are used as recommended by the manufacturer.

The Bessel filter is designed using the normalized poles given below:

| $-\alpha$ | В      |

|-----------|--------|

|           |        |

| 1.3596    | 0.4071 |

| 0.9877    | 1.2476 |

The filter topology used for the active Bessel filter was chosen with two primary factors in mind. First of all, although the unity-gain single-feedback realization has fewer resistors, the capacitor values are not the same. This could potentially lead to difficulties in realizing matched filter responses over the wide data rate range required. The configuration adopted for Canadair uses like capacitor values in the active filter. A second yet minor point is that the op-amps selected for service here do not have to be unity-gain stable.

The comparator U5 is intended to provide symmetric shaping at its output so as to not add to the self-noise level in the timing recovery circuit. Inclusion of this device all but eliminates problems with insufficient input signal level at the bit synchronizer input, and also eliminates potential problems with inadequate slew rate at very low data rates where meta-stable considerations must be addressed.

# 4.2 Loop Filter and Phase Detector

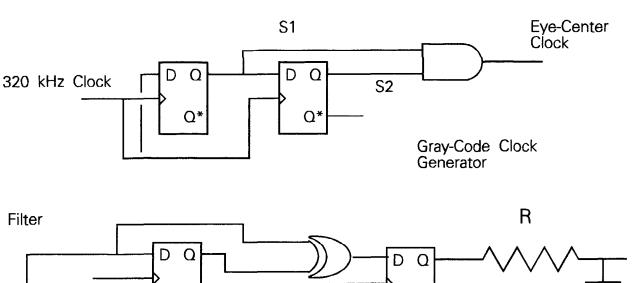

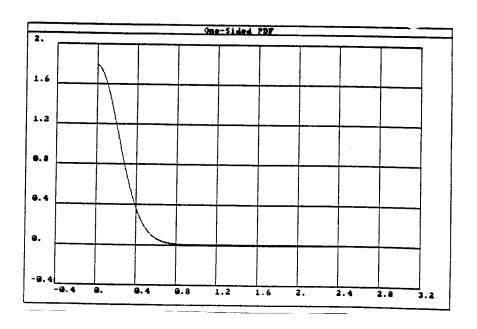

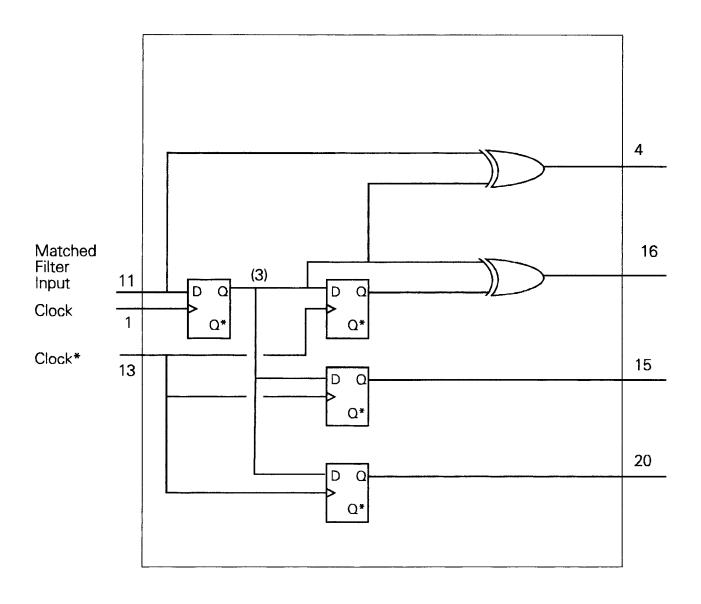

The Hogge phase detector is implemented within the PAL U5. The logic diagram with pin outs of the phase detector are shown in Figure 46. The actual PAL program listing is provided in Figure 47.

Although the CMOS gate stucture should help in keeping rising and falling edge assymmetry small, this will be an increasing concern wherever the bit synchronizer is used at data rates approaching 2 Mbps. These issues must necessarily be investigated for such use. (Although the Hogge topology has been used into the gigabit per second regime, implementation details cannot be taken for granted.)

Care must be exercised in selecting the RC values which immediately follow the phase detector. On one hand, the pulse slew rate is to be decreased into the op-amp by the RC filter, but on the other, loading on the PAL outputs must not be excessive. (This is really only a problem at high data rates.) In order to keep the maximum PAL output currents < 2 mA, R16 and R18 were selected to be 3.01 K. Good tolerance devices are needed in this area so as not to introduce any static tracking errors.

After considerable algebra, the combined transfer function for the Hogge phase detector and U7 circuitry is

$$P(s) - \frac{K_{do}}{2} \frac{1}{1 + s\tau_0} \tag{71}$$

Figure 46. Internal PAL Logic Diagram. (Hogge Phase Detector Portion Only)

```

BSYNC1;

Name

Partno

11/06/90;

Date

Revision

0.1;

Robert J. Wisner;

Designer

Loral Conic;

CANADAIR BIT SYNC BREADBOARD;

Company

Assembly

Location

EP600;

Device

/* PROGRAMMABLE LOGIC FOR DLP BIT SYNC

/*

*/

*/

/** Inputs **/

= CLOCK

/* FROM PIN 8

Pin 13 = CLOCKBAR;

Pin 2 = CTRIN;

Pin 11 = CMPIN;

/* FROM PIN 9

/* FROM 7 STAGE RIPPLE COUNTER

/* FROM COMPARATOR

/* PIN 14,23 ARE SPARE INPUTS */

/** Outputs **/

Pin 3 = U5AQ

= U6AY

/*

/*

Pin 4

= 51

Pin 5

≈ S18AR

≈ U14BQ

≈ 200KOUT

/*

Pin 6

Pin 7

= CLOCKOUT

/* TO PIN 1

Pin 8

Pin 9

= CLKBAROUT

/* TO PIN 13

/* DATA TO TEST POINT /*

= U8AQ

Pin 10

= DATAOUT1

= U6BY

= !U8BQ

Pin 15

Pin 16

/*

Pin 17

= CLOCKOUT1

Pin 18

/* CLOCK TO DLP BUS

Pin 19

= CLKBAROUT1

/* DATA OUT TO DLP BUS

= DATAOUT

Pin 20

Pin 21

≈ U58Q

/* FED BACK INTERNALLY

Pin 22

= SP1

/* SPARE TO

/** Declarations and Intermediate Variable Definitions**/

H = 'B'1;

L = 'B'0;

SP1 = L;

SP2 = L;

SP3 = L;

SP4 = L;

SP5 = L:

/** Logic Equations &=AND #=OR !=NOT $=XOR **/

S1.D = !U14BQ;

S1.CK = CTRIN;

S1BAR.D = U148Q;

S1BAR.CK = CTRIN;

U14BQ.D = S1;

U14BQ.CK = CTRIN;

CLOCKOUT = S1 & U14BQ;

CLKBAROUT = S1BAR & !U14BQ;

CLOCKOUT1 = S1 & U14BQ;

CLKBAROUT1 = S1BAR & !U14BQ;

Figure 47 PAL Listing

CLKBAROUT1 = S1BAR & USAQ.D = CMPIN;

USBQ.D = USAQ;

DATAOUT.D = USAQ;

DATAOUT1.D = USAQ;

U6AY = CMPIN $ U5AQ;

U6AY = U5AQ $ U5BQ;

U8AQ.D = CMPIN;

U8AQ.CK = S1:

U8BQ.D = CMPIN $ U8AQ;

U8BQ.CK = S1BAR;

Chip Diagram

BSYNC1 24 --- × VCC 640

19 --- CLKBAROUT1

18 --- CLOCKOUT1

17 --- 10880

16 --- × U6BY

15 --- × DATAOUT1

14 --- × CLOCKBAR

```

James A. Crawford R&D

December 1990

where

As shown in section 5.0, the VCO sensitivity seen by the loop filter is approximately 617 Hz/volt prior to the resistive divider comprized of  $R_{36}$  and  $R_{37}$ . Including the resistive divider, the leadlag filter sees a VCO sensitivity of only 77 Hz per volt. If a lower lead-lag filter voltage compliance range is needed,  $R_{37}$  could be increased as needed. Neglecting the 1 M resistor shunting  $C_{30}$  in the lead-lag filter, the open\_loop gain function is given by

$$G_{OL}(s) - K_{do} \eta \frac{1}{1 + S \tau_0} \frac{1 + S \tau_2}{S \tau_1} \frac{R_{37}}{R_{36} + R_{37}} \frac{1}{1 + S \tau_3} \frac{K_v}{S}$$

(72)

where

$\eta$  = Transition Density

$\tau_{\rm o}$  = 30.1 usec

$\tau_3$  = 2.89 usec

$K_v = 3877 \text{ rad/sec/volt}$

and  $\tau_1$  and  $\tau_2$  are set differently depending upon whether the synchronizer is in acquisition or tracking mode.

JFET switches are used to switch new values of  $\tau_1$  and  $\tau_2$  in for the two different modes. The source side of each JFET is at the virtual ground provided by U10A which simplifies the gating signals provided to the JFETs Q4 and Q5. Different time constants are used for the JFET gate signals in order to help insure that the switching transient which occurs between acquisition and tracking modes is minimized.

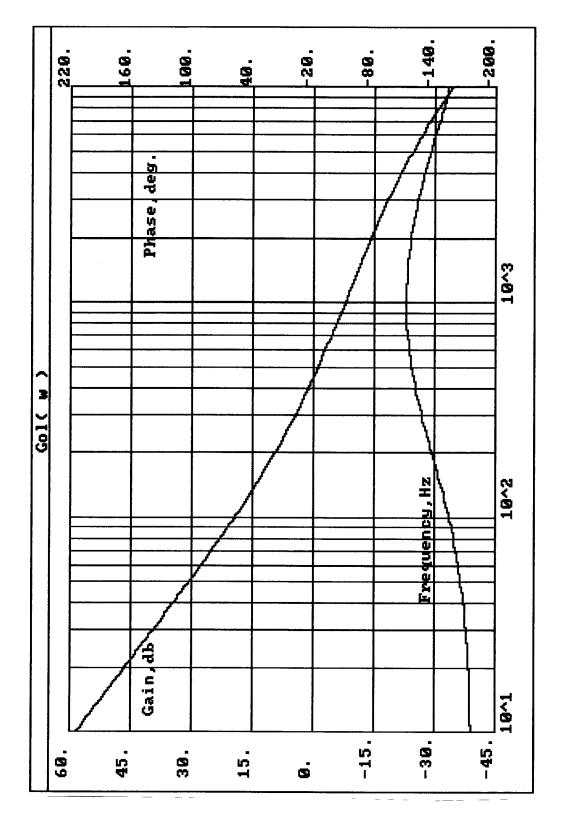

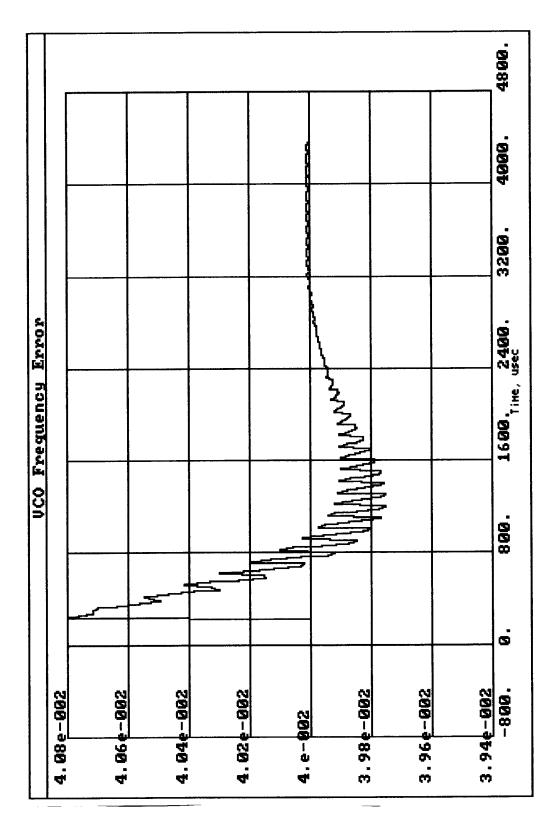

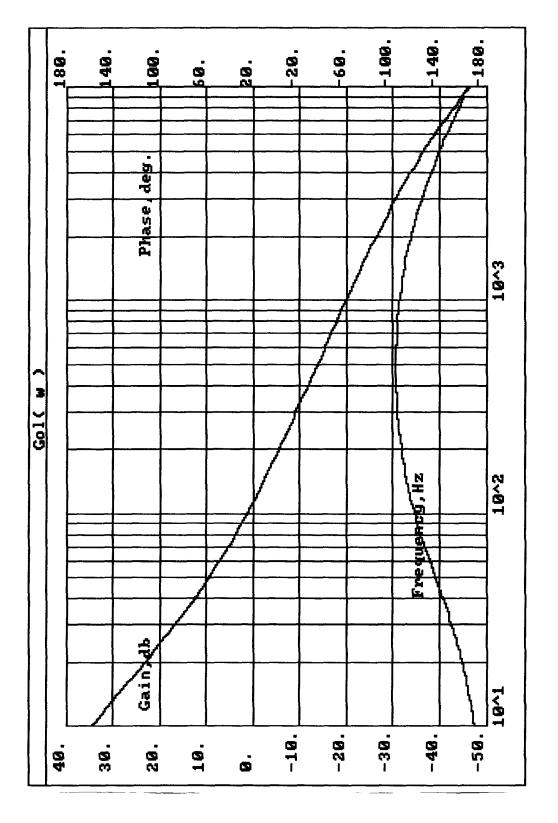

The Bode plot for the bit synchronization loop in acquisition mode is shown in Figure 48 assuming a transition density of 100%. The gain margin is in excess of 30 dB. For the 100% transition density case, the synchronizer can be equivalenced to a frequency synthesis phase-locked loop using a reference frequency of R/2 or 40 kHz. Using this equivalence, the acquisition behavior for the synchronizer in the absence of noise is shown in Figure 49 for a full 1% initial data rate error. Although the sawtooth behavior may look severe, its impact is completely negligible since even a sawtooth peak frequency deviation of 200 Hz is equivalent to roughly 20 log( 200 Hz/(2 40 kHz) ) = -52 dBc at most. The Bode plot for the synchronizer in tracking mode is shown in Figure 50, again assuming a transition density of 100%. An examination of the

James A. Crawford R&D December 1990

Figure 48. Open-loop gain function for the bit synchronizer in acquisition mode assuming a transition density of 100%.

Figure 49. Step-frequency response of the bit synchronizer for a full 1% initial data rate error assuming no noise and a data transition density of 100%.

James A. Crawford R&D December 1990

Figure 50. Open-loop gain characteristic for the bit synchronizer in tracking mode assuming a transition density of 100%.

James A. Crawford R&D December 1990

open-loop gain plots shows that the acquisition and tracking loop bandwidths are as recommended, roughly 400 Hz and 100 Hz for the 0 dB open-loop gain points which correspond to 0.02 R and 0.005 R for the loop  $B_{\scriptscriptstyle L}$  respectively.

# 4.3 Voltage-Controlled Oscillator

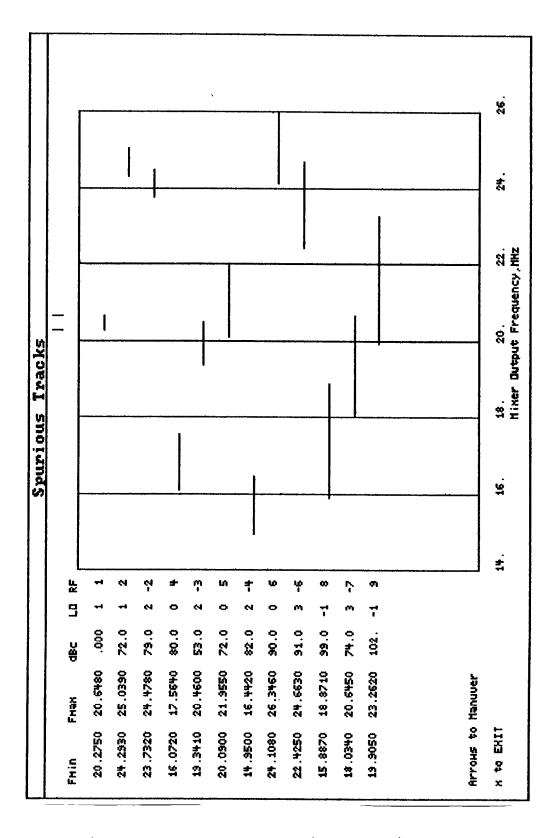

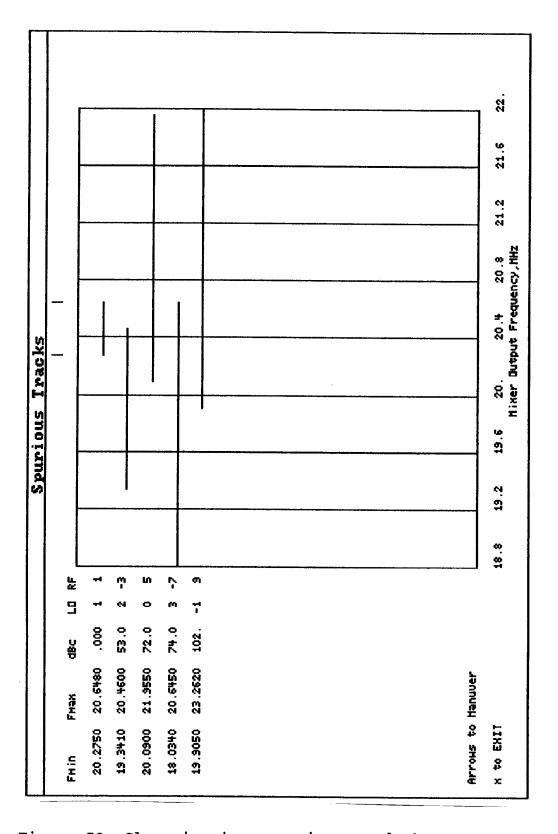

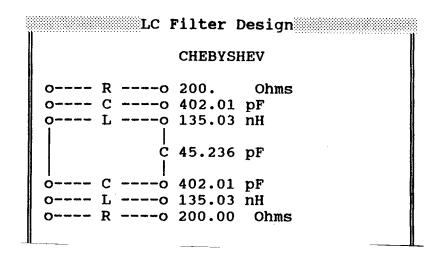

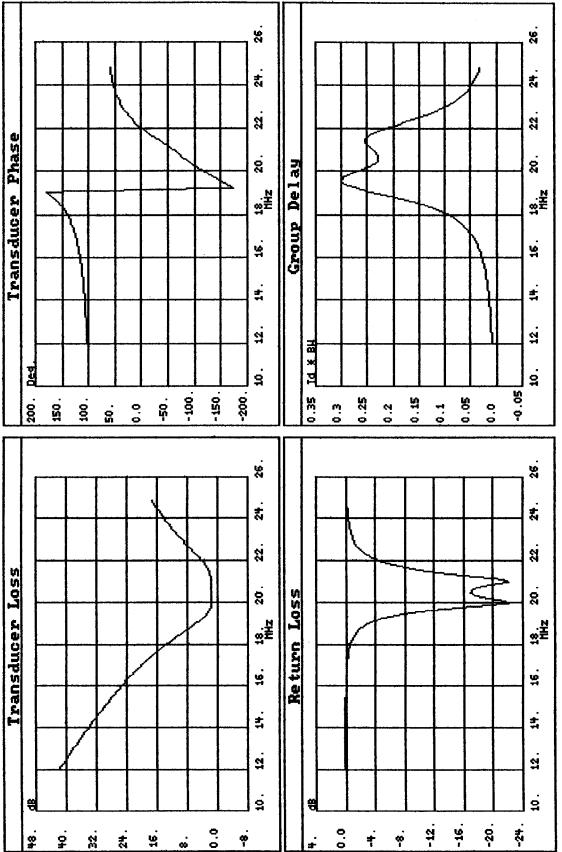

The VCO function as mentioned earlier is a complicated design primarily due to the ±1% data rate uncertainty which it must accomodate while maintaining precise center frequency control in order to keep the required capture range small. The first step involved in designing the VCO was to arrive at a reasonable frequency plan which was relatively spurious free and which resulted in suitably relaxed requirements for the LC oscillator which was to be included. The frequency plan which was arrived at for the Canadair task utilizes a fixed crystal oscillator at 16.257 MHz and an LC oscillator which tunes from 4.02 to 4.43 MHz. This choice of frequencies results in a relatively spurious free frequency output spanning the range of 20.275 MHz to 20.685 MHz ( $\pm 1\%$  coverage). This frequency is divided by 64 and used to create a 4-phase clock whose nominal frequency is 80 kHz. The effective divide by 256 results in a spectral cleanup factor of 48 dB so any spurious components which are present at the mixer output are reduced 48 dB. Details of the mixer spurious analysis parameters are provided in Figure 51 and the actual mixer analysis results are presented in Figures 52 and 53. A generic +7 dBm LO mixer spur table was used to predict the spurious product levels. The analysis reveals that the strongest spurious product which appears is -53 in and of itself is more than adequate for bit synchronizer service. (The local oscillator leakage is expected to be on the order of -35 dBc.) This level is reduced another 48 dB by the forementioned divider action which makes the worst case predicted spur level more on the order of -101 dBc! Mixer spurs should be the least of our concerns for Canadair. The picture will change with each data rate application. For instance, this same frequency plan could be used for a data rate of 2.56 Mbps in which case the predicted spur level would be -53 - 20 log(8) = -74 dBc. This is on the order of 30 dB better than required. These calculations assume an ideal local oscillator waveform and a sinusoidal RF waveform. The RF signal is supplied by the LC oscillator using a single-pole LC tank circuit to remove most of the oscillator harmonics. Since the mixer RF port is linear, elimination of the oscillator harmonics is needed in order to obtain the best mixer performance. The single-pole filter on the LC oscillator output reduces the harmonic outputs to a level where their contribution in the mixer output spectrum is quite negligible even without including the cleanup due to the divide-by-256 element.

The spectral purity of the crystal oscillator is not an issue since it may be considered to be essentially ideal. It is important to check the spectral purity for the LC oscillator however. The LC

James A. Crawford R&D

December 1990